### CS-1994-37

Factors Affecting False Sharing on Page-Granularity Cache-Coherent Shared-Memory Multiprocessors

Vivek Khera

Department of Computer Science Duke University Durham, North Carolina 27708–0129

December 1, 1994

### Factors Affecting False Sharing on Page-Granularity Cache-Coherent Shared-Memory Multiprocessors

by

Vivek Khera

Department of Computer Science Duke University

Approved: December 1, 1994 Carla Schlatter Ellis, Supervisor Kishor S. Trivedi Henry S. Greenside Gopalan Nadathur Joseph W. Kitchen

This is a reformatted version of the dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science in the Graduate School of Duke University.

Copyright © 1994 by Vivek Khera All rights reserved

### Abstract

Efficiently supporting a shared memory paradigm in a large-scale multiprocessor generally involves some form of data caching. One of the drawbacks of caching shared data is the cost of keeping the multiple copies coherent. One source of unnecessary coherency overhead is caused by a problem known as *false sharing*. Unfortunately, the lack of a precise, universally accepted, definition of false sharing hinders research to detect and eliminate the problem.

We articulate our intuitive notion of false sharing and address the problems encountered in previous attempts at defining false sharing. We motivate the importance of a concrete measure by demonstrating that false sharing related coherence overhead comprises a significant portion of the coherence costs in real applications, especially when page-granularity coherence is required. An architecture-independent measure of the false sharing exhibited in a reference trace for cache lines of a specified size is proposed and evaluated experimentally.

The proposed measure attempts to summarize the false sharing impact by approximating some factors and discarding others. The evaluation of this formulation reveals that such summary statistics lose too much information to be of practical use in predicting performance. We use this work to motivate experiments to determine the relative importance of the various workload and architectural factors that affect coherence data traffic. The conclusion from these experiments is that the precise memory reference interleaving order is the most significant factor affecting false sharing coherence data traffic.

Our methodology is to use an execution-driven simulation of specific architectures and applications to generate memory reference traces. The traces are then analyzed off-line.

### ABSTRACT

### Acknowledgements

There are many people who have made my pursuit of this degree possible. Some helped academically and others socially.

First, I'd like to thank my parents for giving me the opportunities while I was growing up to explore my interests. Without their support and encouragement I would never even have attempted this.

Among the many friends I've made during my years in Durham are some of the finest people I know — they have helped make life enjoyable. Dave Kotz and Rick LaRowe as my academic "brothers" have provided many ideas and much guidance in my work, as well as being good friends. Thomas Alexander, Chris Connelly, and Apratim Purakayastha have been invaluable in helping me work through some of the rough spots while conducting this research.

Friday afternoon happy hours with Rick and the other AHH-ers, Dov Bulka, Dave Reed, Owen Astrachan, Jonathan Polito, Varsha Mainkar, and Jitendra Apte provided life with some of its most interesting moments. I thank Deganit Armon, Eric Anderson, and Marge Dietz for the long philosophical conversations about life, the universe, and everything. I also thank Eric for making me camp out for basketball season tickets, especially since I got to see all those awesome home games! Finally, for throwing interesting twists and turns into my life, I want to thank Lars Nyland, Stacy Doyle, and Katya Prince. The Ultimate Frisbee gang at Forest Hills Park have also helped me enjoy my last year in Durham much more.

A very special thank you goes to my second "mom", Carla Schlatter Ellis, for supporting me through the ups and downs of the entire process.

### ACKNOWLEDGEMENTS

# Contents

| $\mathbf{A}$ | Abstract                               |                                                                                                                                                                                                                                                                                                                         |                                                                                                |

|--------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| A            | cknov                                  | wledgements                                                                                                                                                                                                                                                                                                             | $\mathbf{v}$                                                                                   |

| 1            | <b>Intr</b><br>1.1<br>1.2              | coduction         Evidence of the importance of false sharing         Background                                                                                                                                                                                                                                        | <b>1</b><br>1<br>2                                                                             |

| 2            | <b>Pro</b><br>2.1<br>2.2<br>2.3<br>2.4 | <b>posed definition</b> Difficulty of defining false sharing         Definitions for factors         Measures for false sharing         Summary                                                                                                                                                                         | <b>5</b><br>5<br>6<br>8<br>10                                                                  |

| 3            | Exp<br>3.1<br>3.2                      | Derimental Methodology         The simulator         3.1.1         The machine we are modeling         3.1.2         Architecture parameters         3.1.3         Detailed operation of the simulator         Calculating true costs         3.2.1         Invalidate Coherency         3.2.2         Update Coherency | <ol> <li>11</li> <li>11</li> <li>12</li> <li>13</li> <li>14</li> <li>14</li> <li>15</li> </ol> |

| 4            | Wo                                     | rkload description                                                                                                                                                                                                                                                                                                      | 17                                                                                             |

| т            | 4.1                                    | Synthetic programs                                                                                                                                                                                                                                                                                                      | 17<br>17<br>19                                                                                 |

|              | 4.2                                    | Real applications                                                                                                                                                                                                                                                                                                       | 19<br>19<br>19<br>20<br>20                                                                     |

| 5            |                                        | alysis of synthetic workload program execution                                                                                                                                                                                                                                                                          | 21                                                                                             |

|              | $5.1 \\ 5.2 \\ 5.3 \\ 5.4$             | Introduction                                                                                                                                                                                                                                                                                                            | 21<br>23<br>27<br>32                                                                           |

|              | $5.5 \\ 5.6$                           | Normal execution   Discussion                                                                                                                                                                                                                                                                                           | 34<br>34                                                                                       |

| 6  | Ana  | alysis of SPLASH program execution                                                                                                                                               | 37           |

|----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

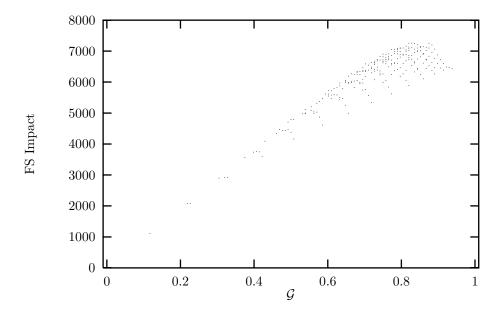

|    | 6.1  | Evaluation of $\mathcal{G}$ as predictor                                                                                                                                         | 37           |

|    |      | 6.1.1 Barnes-Hut                                                                                                                                                                 | 37           |

|    |      | 6.1.2 Cholesky                                                                                                                                                                   | 39           |

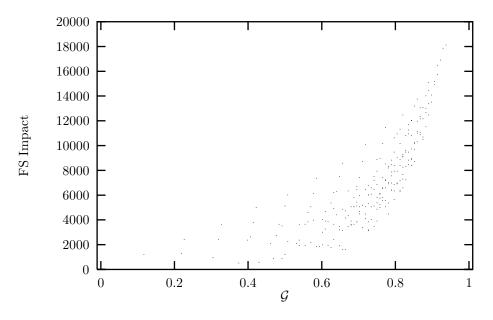

|    |      | 6.1.3 MP3D                                                                                                                                                                       | 43           |

|    |      | 6.1.4 Water                                                                                                                                                                      | 47           |

|    |      | 6.1.5 Discussion                                                                                                                                                                 | 50           |

|    | 6.2  | Evaluation of $\mathcal{G}'$ as predictor $\ldots \ldots \ldots$ | 52           |

|    |      | 6.2.1 Barnes-Hut                                                                                                                                                                 | 52           |

|    |      | 6.2.2 Cholesky                                                                                                                                                                   | 52           |

|    |      | 6.2.3 MP3D                                                                                                                                                                       | 52           |

|    |      | 6.2.4 Water                                                                                                                                                                      | 55           |

|    |      | 6.2.5 Discussion                                                                                                                                                                 | 55           |

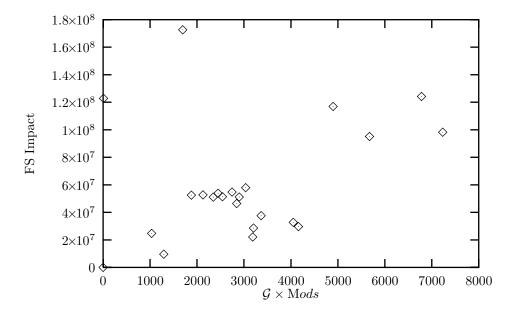

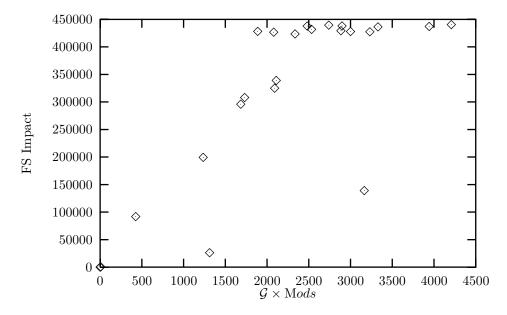

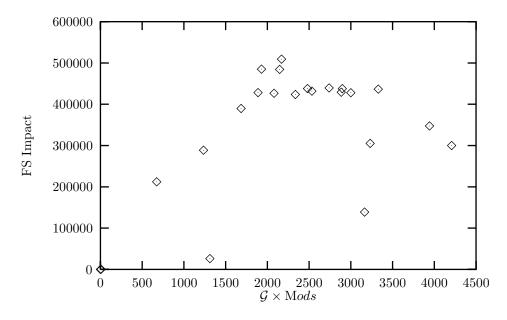

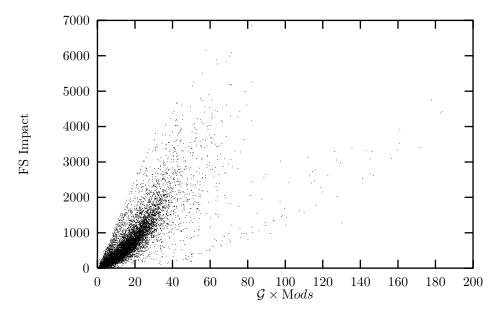

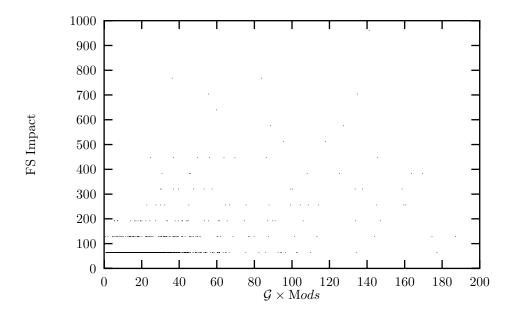

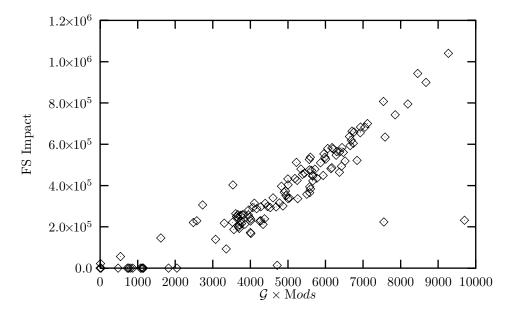

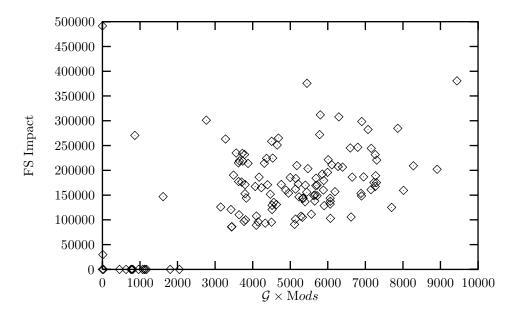

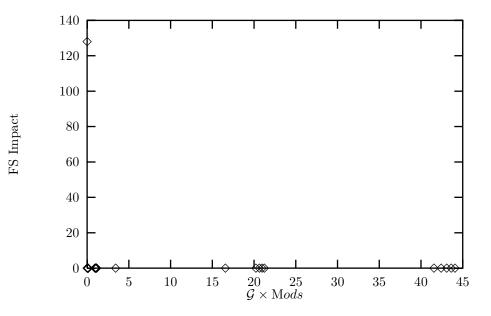

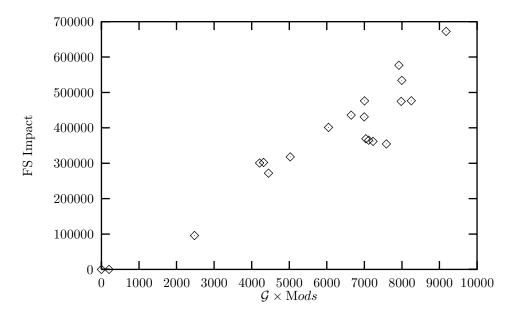

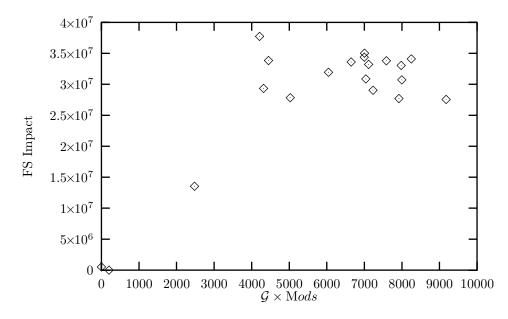

|    | 6.3  | Evaluation of $\mathcal{G} \times Mods$ as predictor                                                                                                                             | 55           |

|    |      | 6.3.1 Barnes-Hut                                                                                                                                                                 | 56           |

|    |      | 6.3.2 Choleksy                                                                                                                                                                   | 56           |

|    |      | 6.3.3 MP3D                                                                                                                                                                       | 62           |

|    |      | 6.3.4 Water                                                                                                                                                                      | 65           |

|    |      | 6.3.5 Discussion                                                                                                                                                                 | 65           |

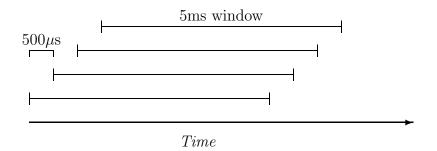

|    | 6.4  | Limiting evaluation to phases                                                                                                                                                    | 68           |

|    |      | 6.4.1 Barnes-Hut                                                                                                                                                                 | 68           |

|    |      | 6.4.2 Cholesky                                                                                                                                                                   | 72           |

|    |      | 6.4.3 MP3D                                                                                                                                                                       | 79           |

|    |      | 6.4.4 Water                                                                                                                                                                      | 82           |

|    |      | 6.4.5 Discussion                                                                                                                                                                 | 89           |

|    | 6.5  | Summary                                                                                                                                                                          | 89           |

| 7  | Eva  | luation of factors                                                                                                                                                               | 91           |

| •  | 7.1  | Experiment design                                                                                                                                                                | 91           |

|    |      | 7.1.1 Background                                                                                                                                                                 | 91           |

|    |      | 7.1.2 Details of the experiment                                                                                                                                                  | 92           |

|    | 7.2  | Results                                                                                                                                                                          | 93           |

|    |      | 7.2.1 Four processor evaluation                                                                                                                                                  | 93           |

|    |      | 7.2.2 Sixteen processor evaluation                                                                                                                                               | 96           |

|    | 7.3  | Discussion                                                                                                                                                                       | 97           |

| 8  | Cor  | clusions and future research                                                                                                                                                     | 01           |

| 0  | 8.1  |                                                                                                                                                                                  | 101          |

|    | 8.2  |                                                                                                                                                                                  | $101 \\ 102$ |

|    | -    | •                                                                                                                                                                                | -            |

| Bi | ogra | phy 1                                                                                                                                                                            | 07           |

# List of Figures

| 1.1  | Coherence data bytes transferred (real applications)                          | 3  |

|------|-------------------------------------------------------------------------------|----|

| 3.1  | Idealized NUMA shared memory architecture                                     | 12 |

| 4.1  | Memory reference code for synth-FS                                            | 18 |

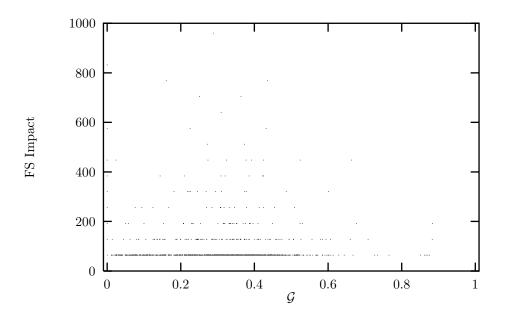

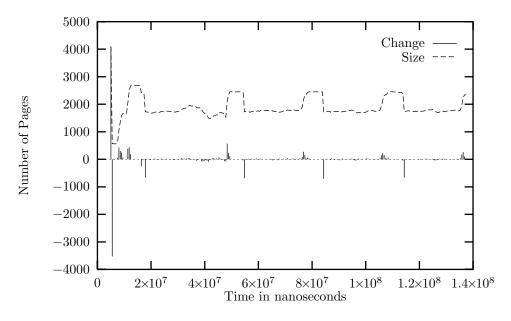

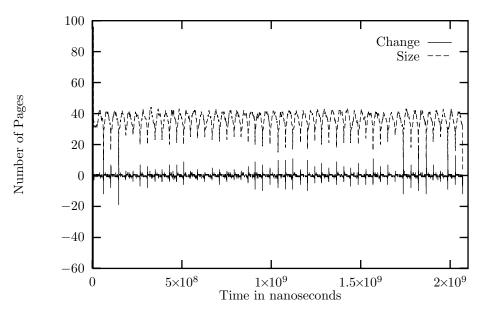

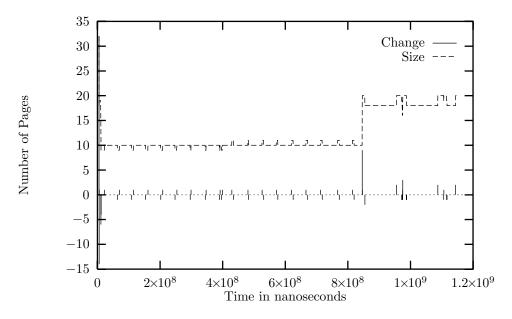

| 5.1  | synth-FS-s-n10, 64-byte page, update coherency                                | 22 |

| 5.2  | synth-FS-s-n10, 64-byte page, invalidate coherency                            | 22 |

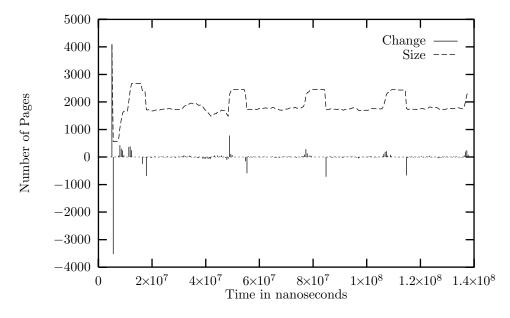

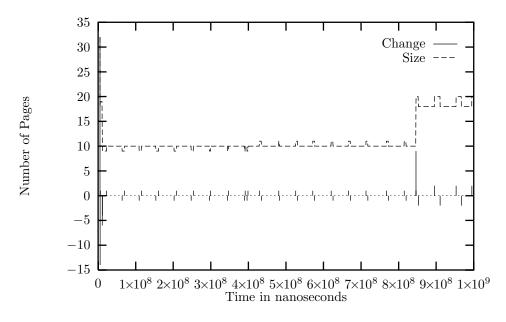

| 5.3  | synth-FS-s-n10, 8k-byte page, update coherency                                | 23 |

| 5.4  | synth-FS-s-n10, 8k-byte page, expiring update coherency (clipped)             | 24 |

| 5.5  | synth-FS-s-n10, 8k-byte page, invalidate coherency                            | 24 |

| 5.6  | synth-FS+PSS-s-n10, 64-byte page, update coherency                            | 25 |

| 5.7  | synth-FS+PSS-s-n10, 64-byte page, invalidate coherency                        | 26 |

| 5.8  | synth-FS+PSS-s-n10, 8k-byte page, update coherency                            | 26 |

| 5.9  | synth-FS+PSS-s-n10, 8k-byte page, invalidate coherency                        | 27 |

| 5.10 |                                                                               | 28 |

|      | synth-FS-n10, 8k-byte page, invalidate coherency                              | 28 |

| 5.12 | synth-FS-n10, 64-byte page, update coherency                                  | 29 |

|      | synth-FS-n10, 8k-byte page, update coherency                                  | 29 |

|      | synth-FS+PSS-n10, 64-byte page, update coherency                              | 30 |

| 5.15 | synth-FS+PSS-n10, 8k-byte page, update coherency                              | 30 |

|      | synth-FS+PSS-n10, 64-byte page, invalidate coherency                          | 31 |

|      | synth-FS+PSS-n10, 8k-byte page, invalidate coherency                          | 31 |

|      | synth-FS-s, 64-byte page, invalidate coherency                                | 32 |

|      | synth-FS-s, 8k-byte page, invalidate coherency                                | 33 |

|      | synth-FS+PSS-s, 64-byte page, invalidate coherency                            | 33 |

|      | synth-FS+PSS-s, 8k-byte page, invalidate coherency                            | 34 |

|      | synth-FS, 8k-byte page, invalidate coherency                                  | 35 |

| 5.23 | synth-FS, 64-byte page, invalidate coherency                                  | 35 |

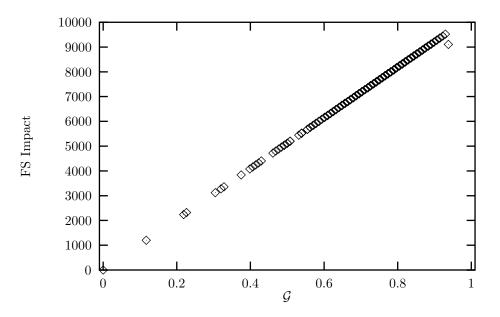

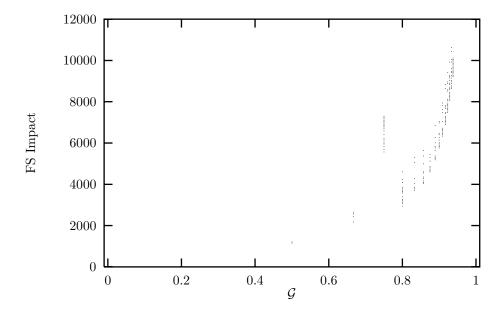

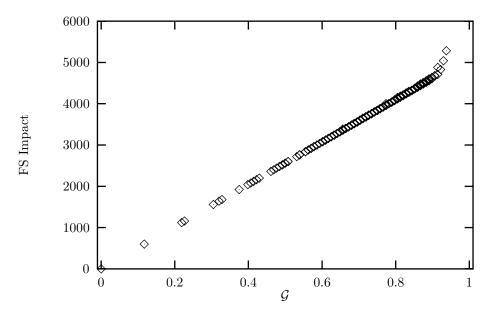

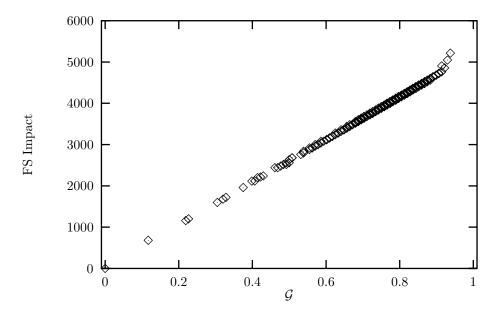

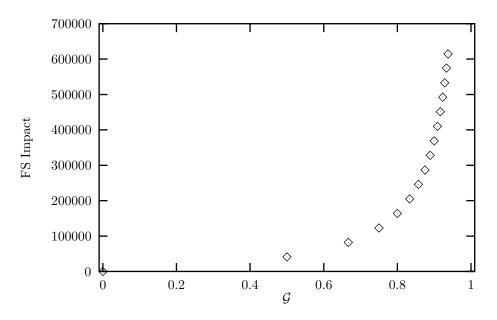

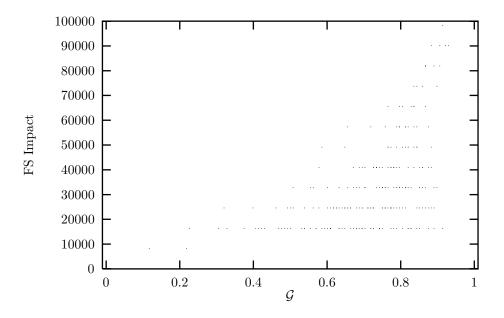

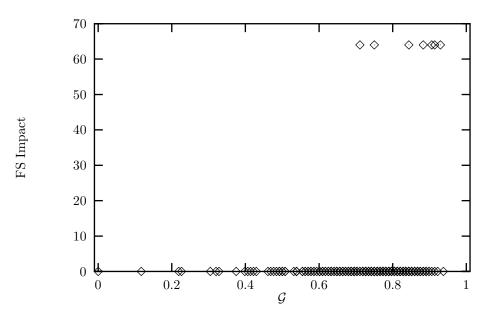

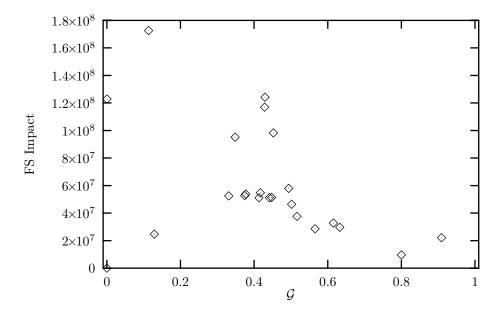

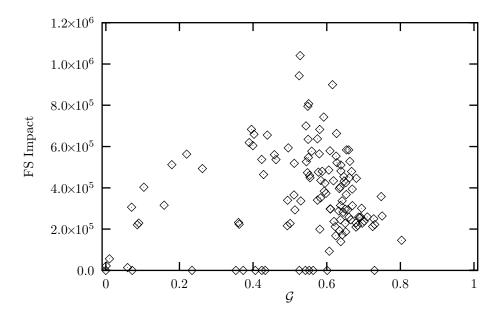

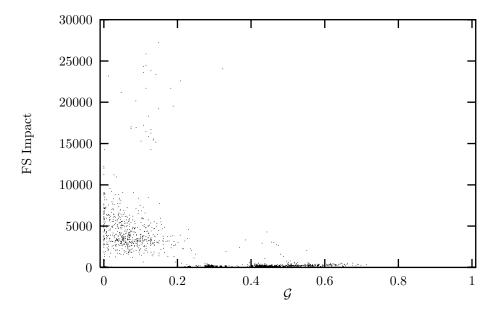

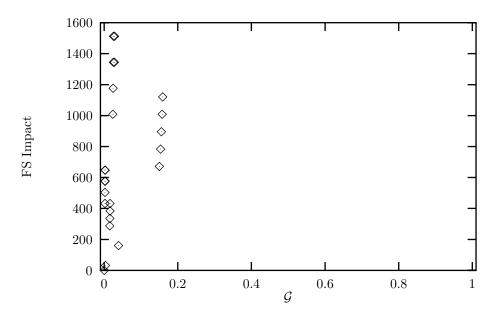

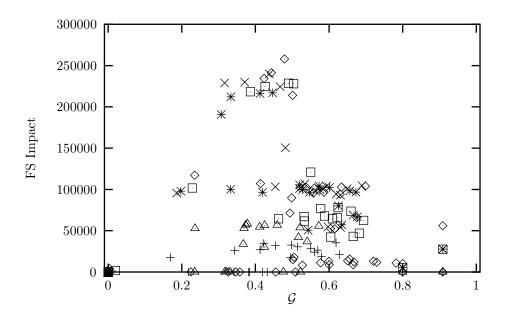

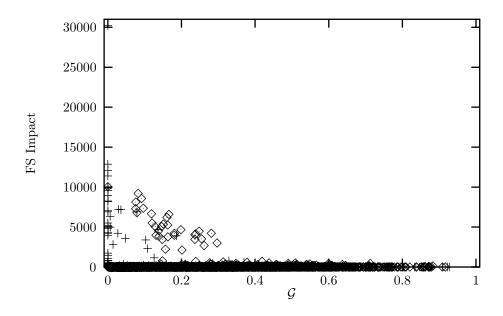

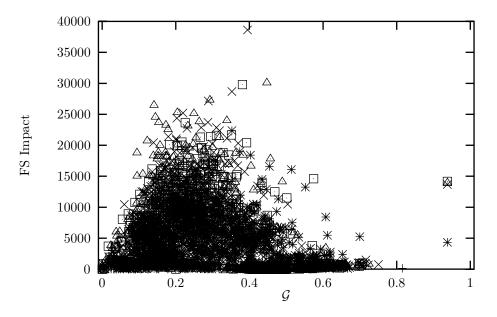

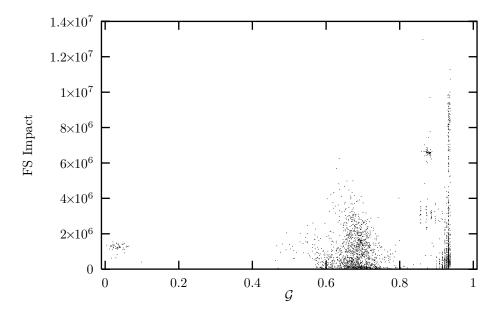

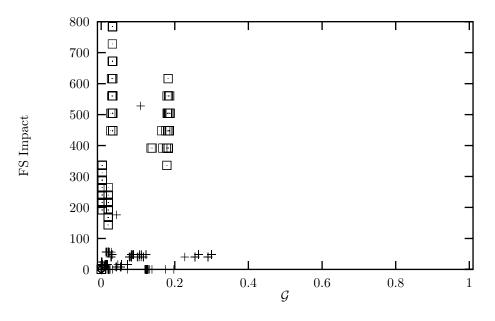

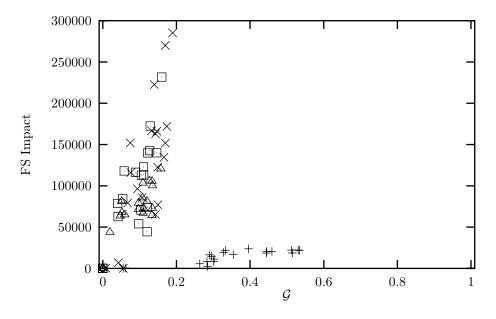

| 6.1  | Barnes-Hut, 64-byte page, update coherency $(\mathcal{G})$                    | 38 |

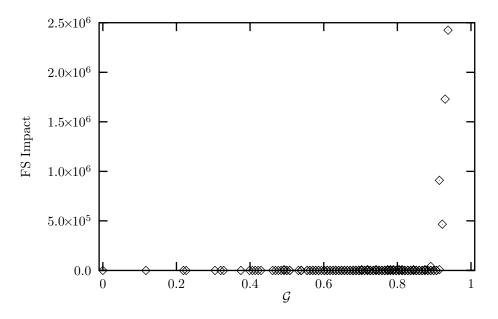

| 6.2  | Barnes-Hut, 64-byte page, invalidate coherency $(\mathcal{G})$ (clipped)      | 39 |

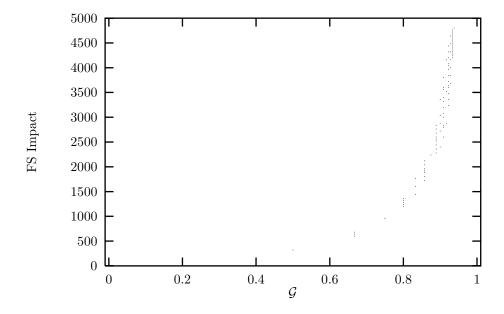

| 6.3  | Barnes-Hut, 8k-byte page, update coherency $(\mathcal{G})$                    | 40 |

| 6.4  | Barnes-Hut, 8k-byte page, invalidate coherency $(\mathcal{G})$                | 40 |

| 6.5  | Barnes-Hut, 64-byte page, expiring update coherency $(\mathcal{G})$ (clipped) | 41 |

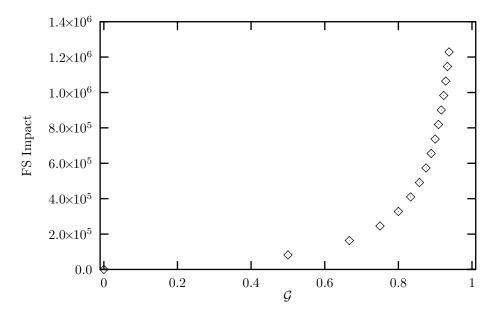

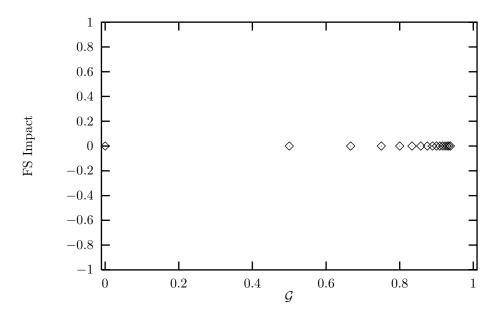

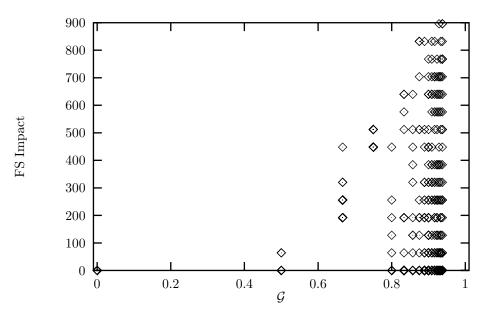

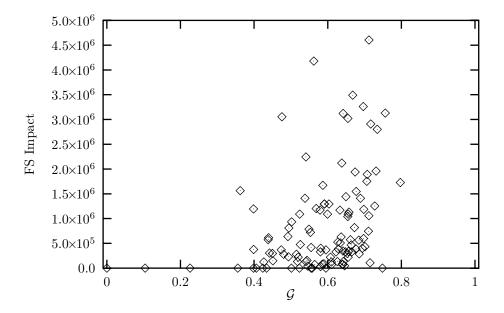

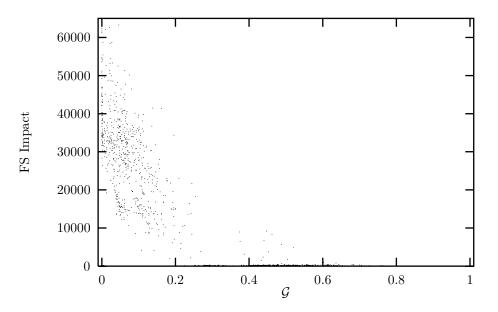

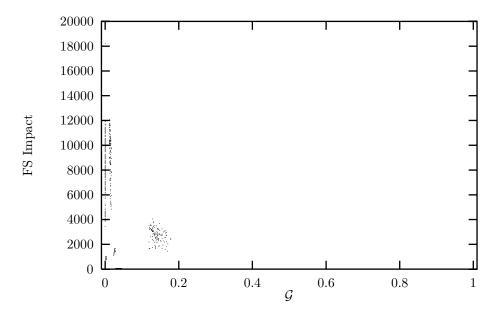

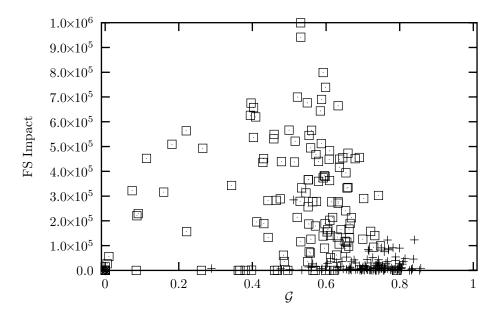

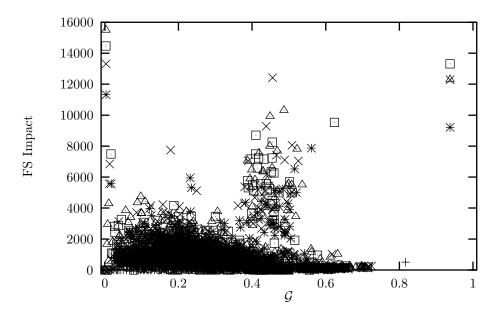

| 6.6  | Cholesky, 64-byte page, update coherency $(\mathcal{G})$                      | 42 |

| 6.7  | Cholesky, 64-byte page, expiring update coherency $(\mathcal{G})$ (clipped)   | 42 |

| 6.8  | Cholesky, 64-byte page, invalidate coherency $(\mathcal{G})$ (clipped)        | 43 |

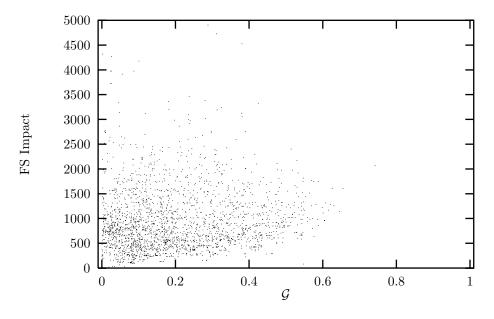

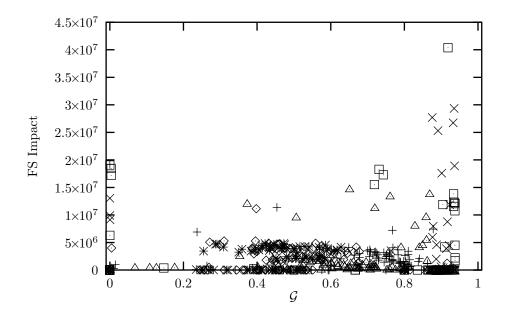

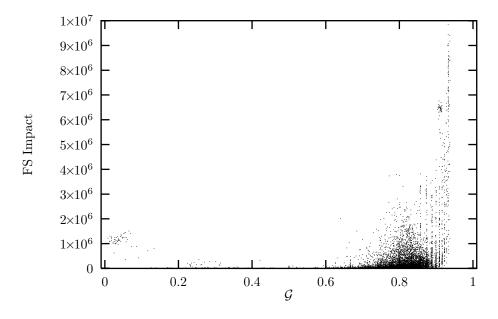

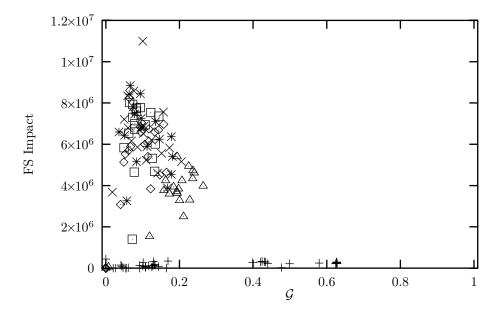

| 6.9  | Cholesky, 8k-byte page, update coherency $(\mathcal{G})$                      | 44 |

| 6.10 |                                                                               | 44 |

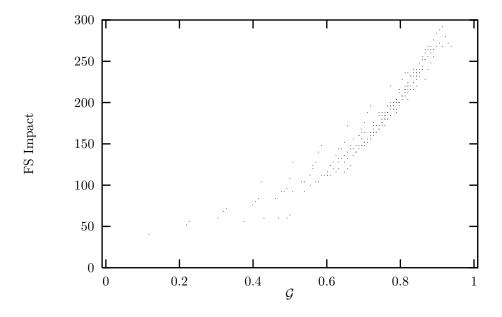

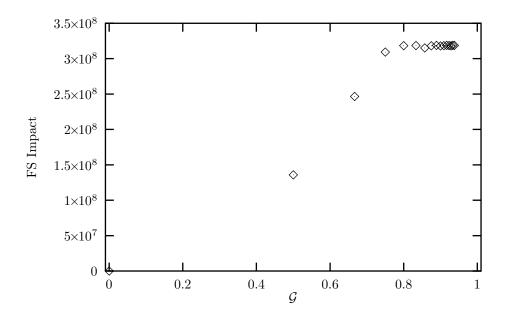

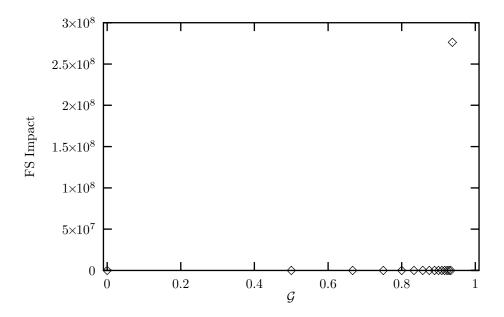

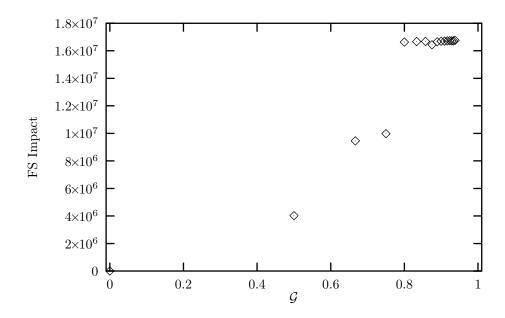

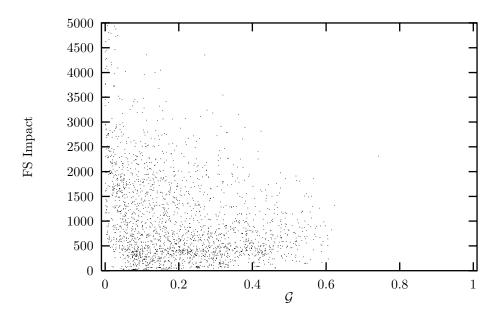

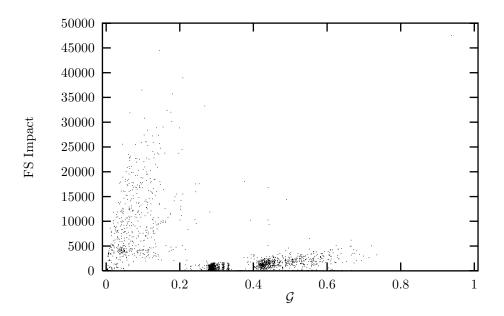

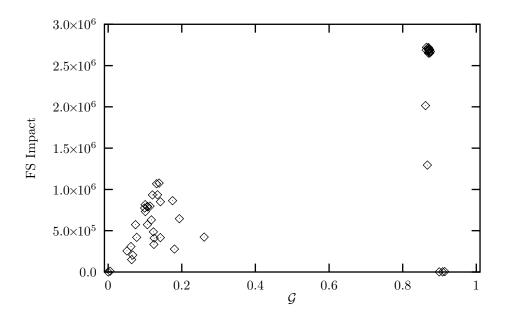

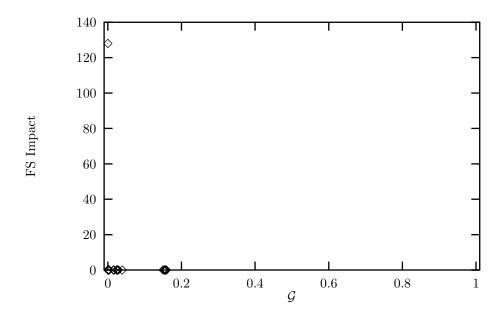

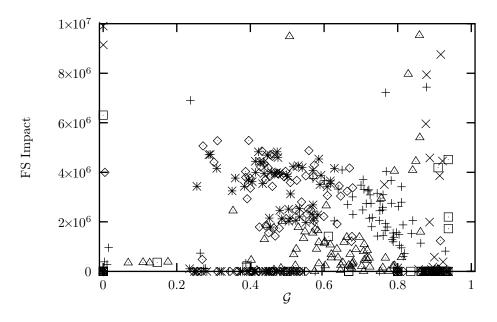

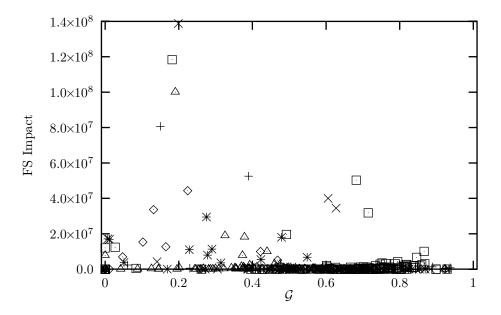

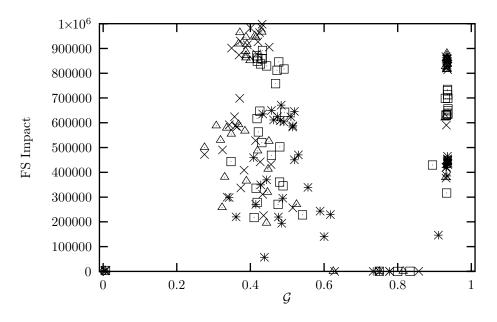

| 6.11 | Mp3d, 64-byte page, update coherency $(\mathcal{G})$                          | 45 |

| 6.12 | Mp3d, 64-byte page, invalidate coherency $(\mathcal{G})$ (clipped)                                                                                                                  | 46       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | Mp3d, 64-byte page, expiring update coherency $(\mathcal{G})$ (clipped)                                                                                                             | 46       |

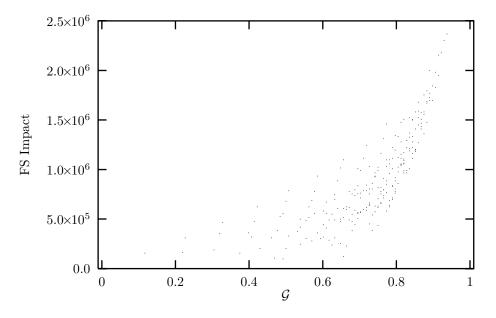

| 6.14 | Mp3d, 8k-byte page, update coherency $(\mathcal{G})$                                                                                                                                | 47       |

| 6.15 | Mp3d, 8k-byte page, invalidate coherency $(\mathcal{G})$                                                                                                                            | 48       |

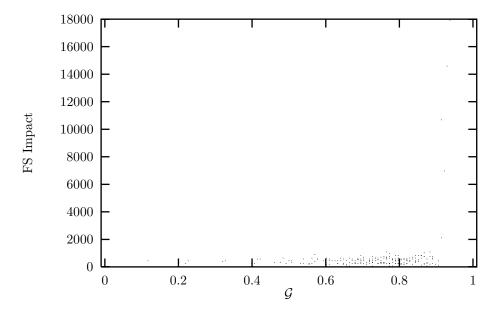

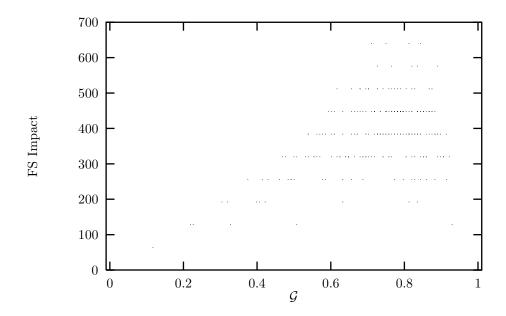

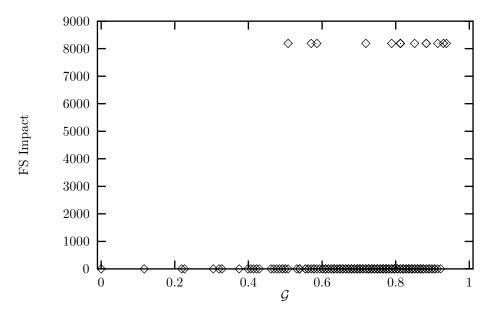

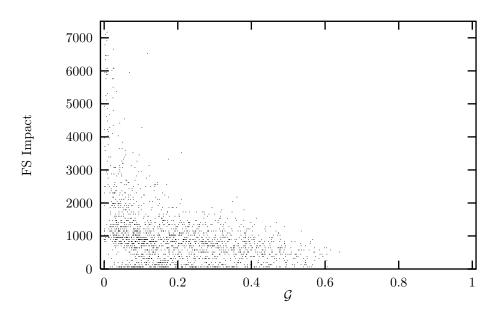

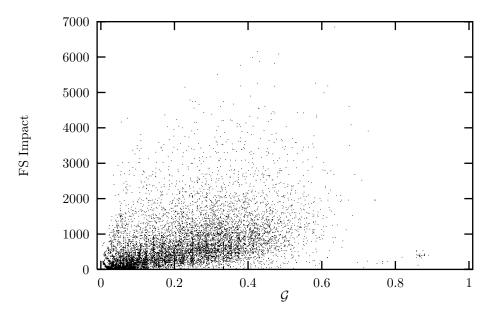

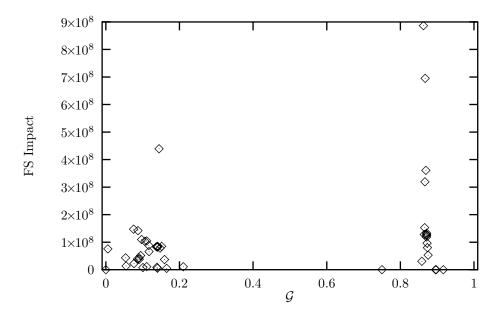

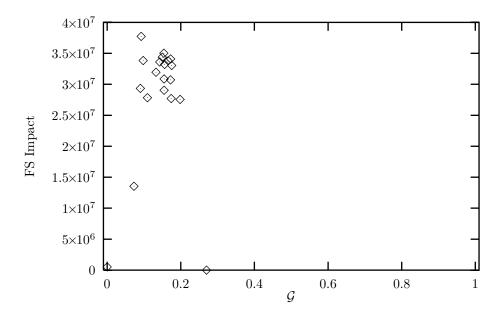

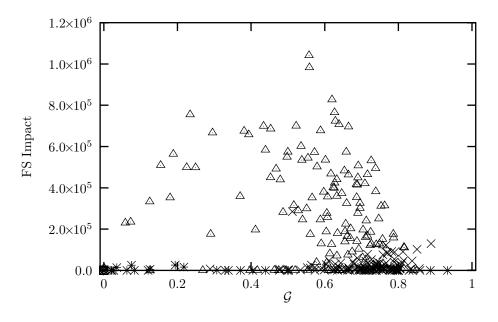

|      | Water, 64-byte page, update coherency $(\mathcal{G})$                                                                                                                               | 49       |

| 6.17 | Water, 64-byte page, expiring update coherency $(\mathcal{G})$                                                                                                                      | 49       |

|      | Water, 64-byte page, invalidate coherency $(\mathcal{G})$                                                                                                                           | 50       |

|      | Water, 8k-byte page, update coherency $(\mathcal{G})$                                                                                                                               | 51       |

| 6.20 | Water, 8k-byte page, invalidate coherency $(\mathcal{G})$                                                                                                                           | 51       |

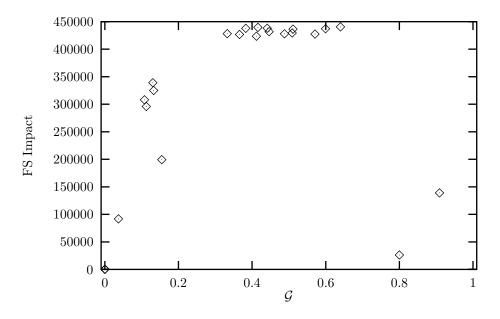

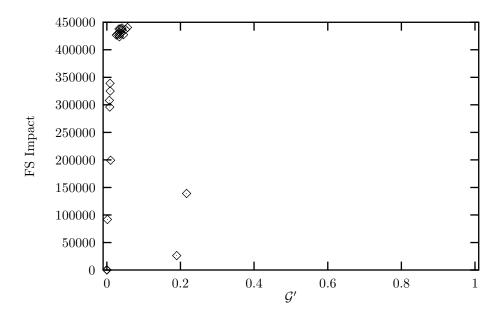

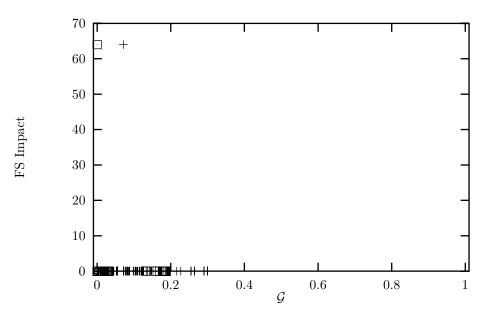

|      | Barnes-Hut, 8k-byte page, update coherency $(\mathcal{G}')$                                                                                                                         | 52       |

|      | Barnes-Hut, 8k-byte page, invalidate coherency $(\mathcal{G}')$                                                                                                                     | 53       |

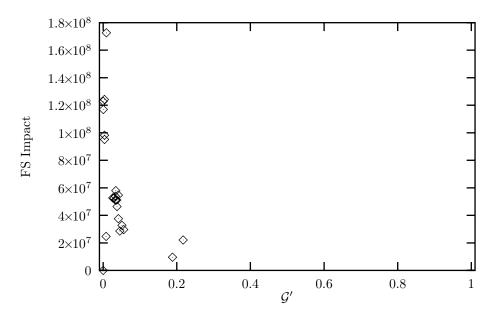

| 6.23 | Cholesky, 8k-byte page, update coherency $(\mathcal{G}')$                                                                                                                           | 53       |

| 6.24 | Cholesky, 8k-byte page, invalidate coherency $(\mathcal{G}')$ (clipped)                                                                                                             | 54       |

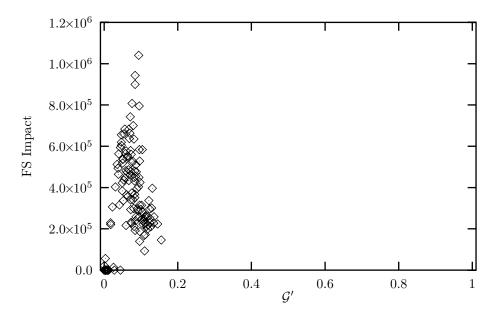

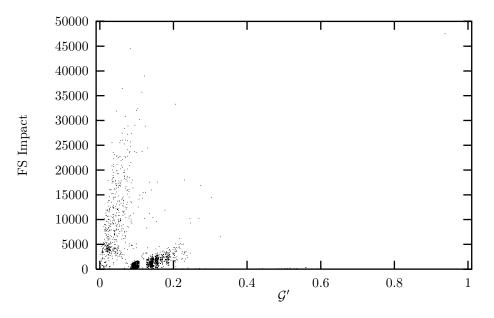

| 6.25 | Mp3d, 64-byte page, update coherency $(\mathcal{G}')$                                                                                                                               | 54       |

|      | Mp3d, 64-byte page, invalidate coherency $(\mathcal{G}')$ (clipped)                                                                                                                 | 55       |

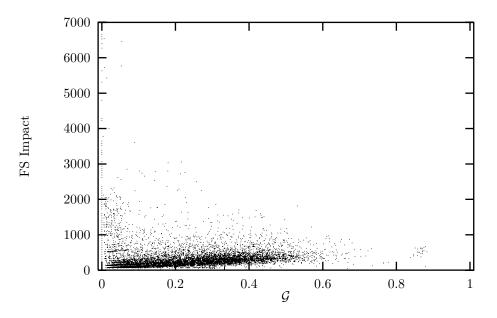

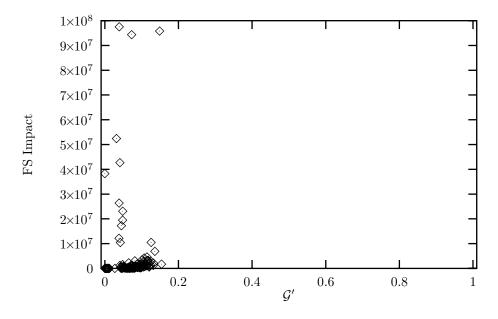

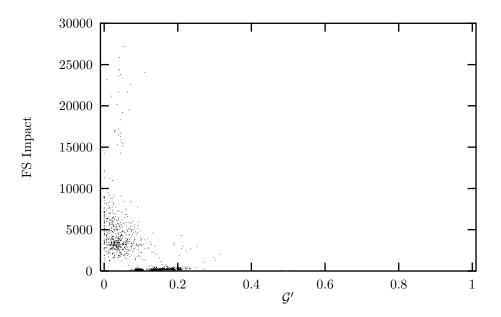

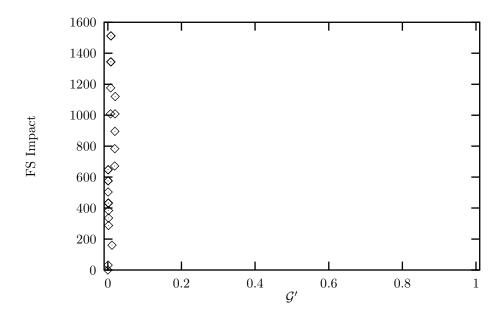

|      | Water, 64-byte page, update coherency $(\mathcal{G}')$                                                                                                                              | 56       |

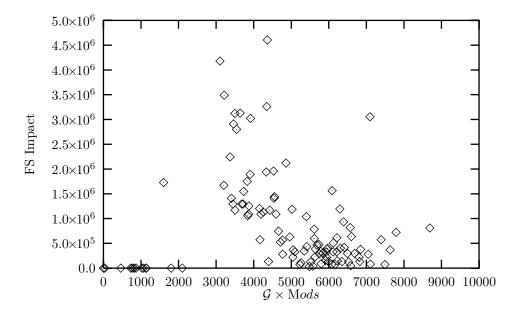

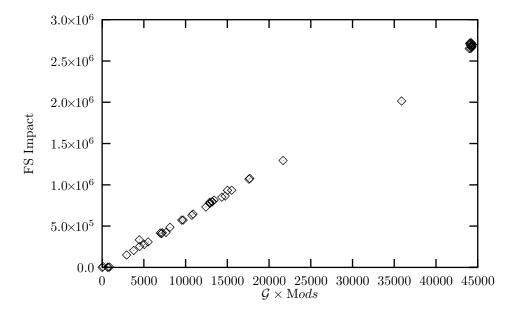

|      | Barnes-Hut, 64-byte page, invalidate coherency $(\mathcal{G} \times Mods)$                                                                                                          | 57       |

|      | Barnes-Hut, 64-byte page, update coherency $(\mathcal{G} \times Mods)$                                                                                                              | 57       |

|      | Barnes-Hut, 8k-byte page, invalidate coherency $(\mathcal{G} \times Mods)$                                                                                                          | 58       |

|      | Barnes-Hut, 8k-byte page, update coherency $(\mathcal{G} \times Mods)$                                                                                                              | 58       |

|      | Barnes-Hut, 8k-byte page, expiring update coherency $(\mathcal{G} \times Mods)$                                                                                                     | 59       |

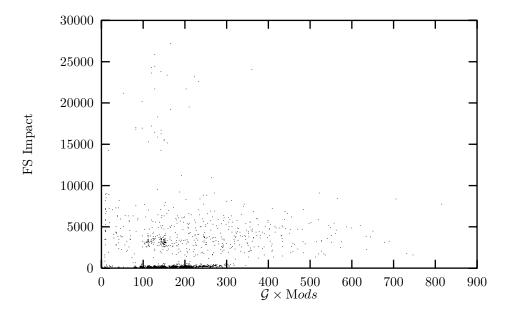

|      | Cholesky, 64-byte page, update coherency $(\mathcal{G} \times Mods)$                                                                                                                | 59       |

|      | Cholesky, 64-byte page, invalidate coherency ( $\mathcal{G} \times Mods$ )                                                                                                          | 60       |

|      | Cholesky, 8k-byte page, update coherency $(\mathcal{G} \times Mods)$                                                                                                                | 60       |

|      | Cholesky, 8k-byte page, expiring update coherency ( $\mathcal{G} \times Mods$ )                                                                                                     | 61       |

|      | Cholesky, 8k-byte page, invalidate coherency ( $\mathcal{G} \times Mods$ )                                                                                                          | 61       |

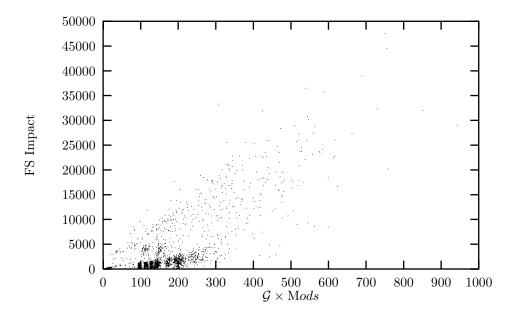

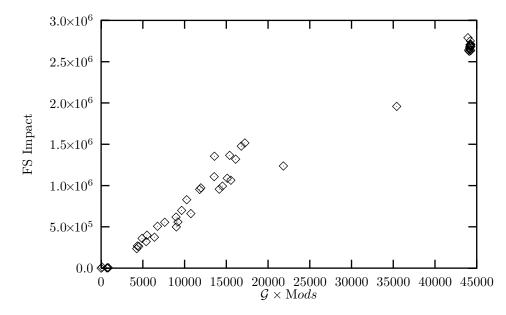

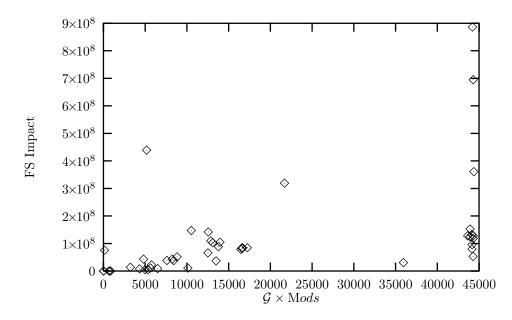

|      | Mp3d, 64-byte page, update coherency $(\mathcal{G} \times Mods)$                                                                                                                    | 62       |

|      | Mp3d, 64-byte page, expiring update coherency ( $\mathcal{G} \times Mods$ ) (clipped)                                                                                               | 63       |

|      | Mp3d, 64-byte page, invalidate coherency ( $\mathcal{G} \times Mods$ ) (clipped)                                                                                                    | 63       |

|      | Mp3d, 8k-byte page, update coherency ( $\mathcal{G} \times Mods$ )                                                                                                                  | 64       |

|      | Mp3d, 8k-byte page, expiring update coherency $(\mathcal{G} \times Mods)$                                                                                                           | 64       |

|      | Mp3d, 8k-byte page, invalidate coherency ( $\mathcal{G} \times Mods$ )                                                                                                              | 65       |

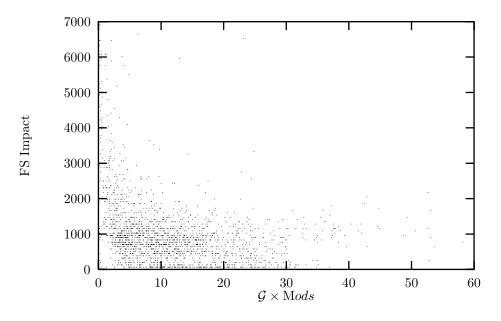

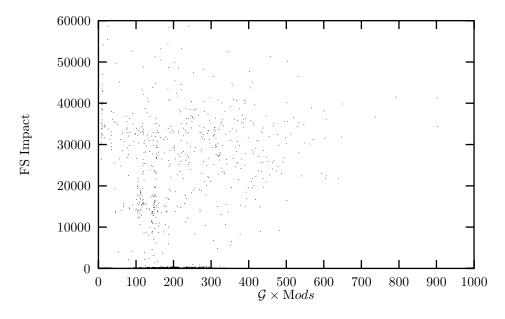

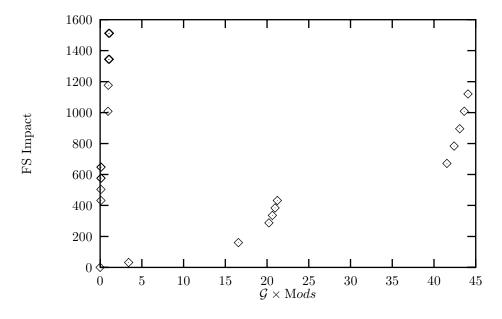

|      | Water, 64-byte page, update coherency $(\mathcal{G} \times Mods)$                                                                                                                   | 66       |

|      | Water, 64-byte page, invalidate coherency ( $\mathcal{G} \times Mods$ )                                                                                                             | 66       |

|      | Water, 8k-byte page, update coherency $(\mathcal{G} \times Mods)$                                                                                                                   | 67       |

|      | Water, 8k-byte page, invalidate coherency ( $\mathcal{G} \times Mods$ )                                                                                                             | 67       |

|      | Overlapping windows for working set calculations                                                                                                                                    | 68       |

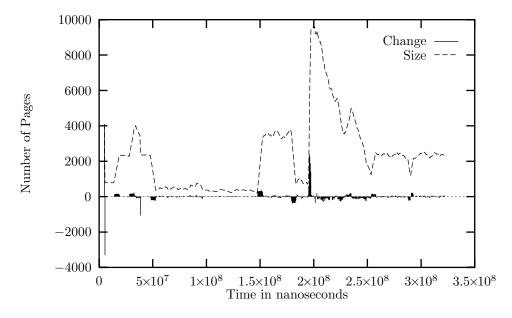

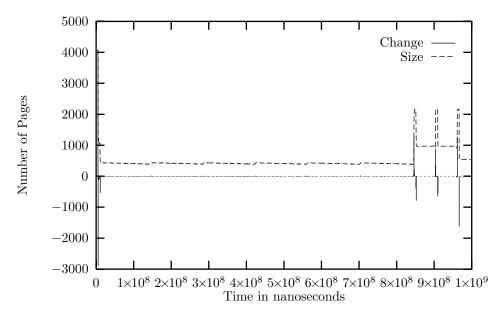

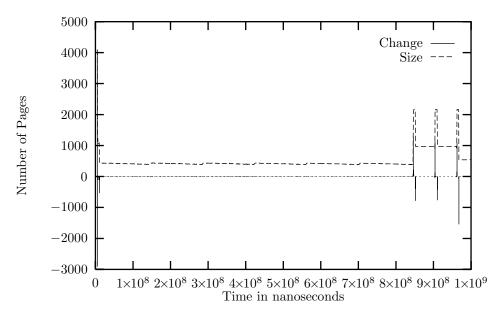

|      | Barnes-Hut working set size, 5ms window (U64)                                                                                                                                       | 69       |

|      | Barnes-Hut working set size, 5ms window (I64)                                                                                                                                       | 69       |

|      | Barnes-Hut working set size, 5ms window (ISI)                                                                                                                                       | 70       |

|      | Barnes-Hut working set size, 5ms window (U8k)                                                                                                                                       | 70       |

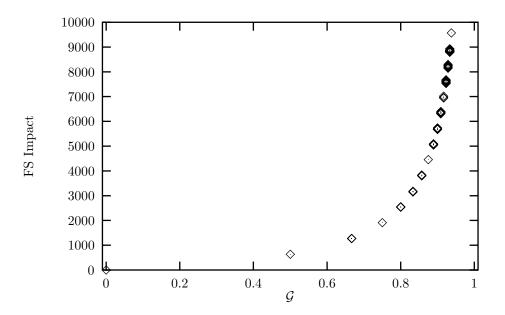

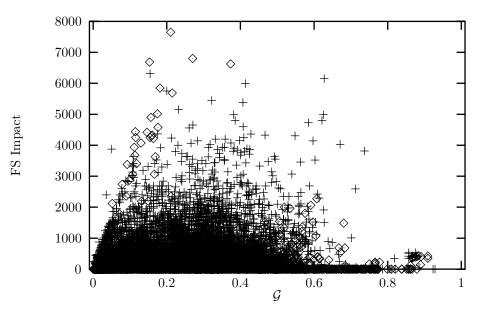

|      | Barnes-Hut, impact of $\mathcal{G}$ , 20ms window (U8k)                                                                                                                             | 71       |

|      | Barnes-Hut, impact of $\mathcal{G}$ , 20ms window (I8k)                                                                                                                             | 72       |

|      | Barnes-Hut, impact of $\mathcal{G}$ , 20ms window (ISk) (clipped)                                                                                                                   | 73       |

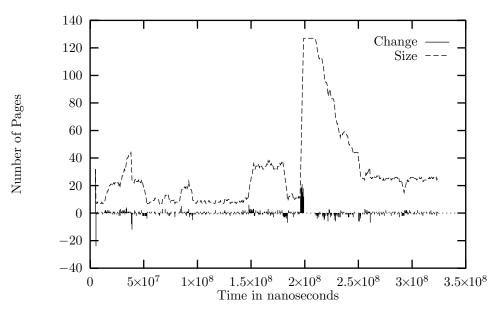

|      | Cholesky working set size, 5ms window (I64)                                                                                                                                         | 73       |

|      | Cholesky working set size, 5ms window (164)                                                                                                                                         | 74       |

|      | Cholesky working set size, 5ms window (U8k)                                                                                                                                         | 74       |

|      | Cholesky working set size, 5ms window (USK)                                                                                                                                         | 74 75    |

|      | Cholesky working set size, sins window (16k) $\ldots \ldots \ldots$ | 75 75    |

|      | Cholesky, impact of $\mathcal{G}$ , 100ms window (164) (clipped)                                                                                                                    | 75<br>76 |

|      |                                                                                                                                                                                     |          |

|      | Cholesky, impact of $\mathcal{G}$ , 100ms window (U8k)                                                                                                                              | 77<br>77 |

| 0.03 | Cholesky, impact of $\mathcal{G}$ , 100ms window (I8k)                                                                                                                              | 77       |

| 6.64       | Cholesky, impact of $\mathcal{G}$ , 50ms window (U8k)                                                                                      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 6.65       | Cholesky, impact of $\mathcal{G}$ , 50ms window (I8k)                                                                                      |

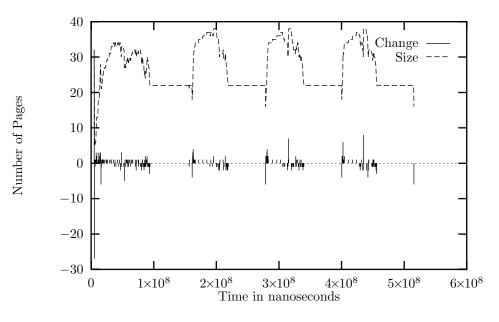

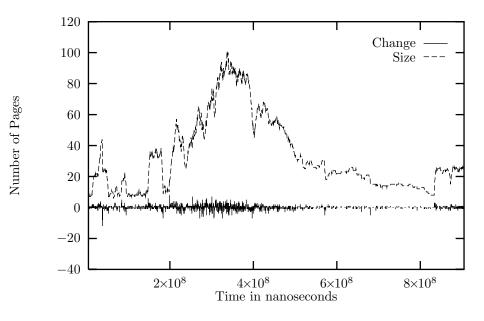

| 6.66       | Mp3d working set size, $5ms$ window (U64)                                                                                                  |

|            | Mp3d working set size, 5ms window (I64) 80                                                                                                 |

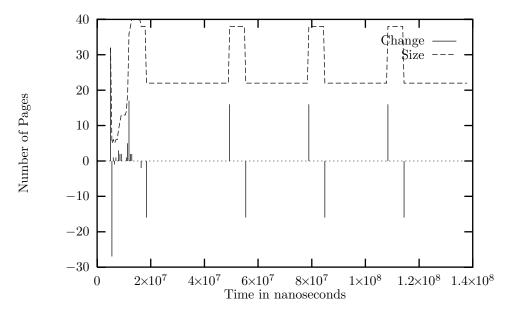

|            | Mp3d working set size, 5ms window $(U8k)$                                                                                                  |

|            | Mp3d working set size, 5ms window (I8k) 81                                                                                                 |

|            | Mp3d, impact of $\mathcal{G}$ , 10ms window (U64)                                                                                          |

|            | Mp3d, impact of $\mathcal{G}$ , 10ms window (I64)                                                                                          |

|            | Mp3d, impact of $\mathcal{G}$ , 10ms window (U8k) $\ldots \ldots 33$ |

|            | Mp3d, impact of $\mathcal{G}$ , 40ms window (I8k)                                                                                          |

|            | Mp3d, impact of $\mathcal{G}$ , 10ms window (I8k)                                                                                          |

|            | Water working set size, 5ms window (U64)                                                                                                   |

|            | Water working set size, 5ms window (I64)                                                                                                   |

|            | Water working set size, 5ms window (I8k) 85                                                                                                |

|            | Water working set size, 5ms window (U8k)                                                                                                   |

|            | Water, impact of $\mathcal{G}$ , 150ms window (U64) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots $ 87                          |

| 6.80       | Water, impact of $\mathcal{G}$ , 150ms window (I64)                                                                                        |

| 6.81       | Water, impact of $\mathcal{G}$ , 50ms window (U8k)                                                                                         |

| 6.82       | Water, impact of $\mathcal{G}$ , 50ms window (I8k)                                                                                         |

| <b>∀</b> 1 |                                                                                                                                            |

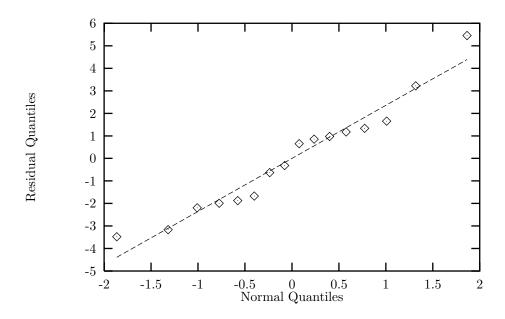

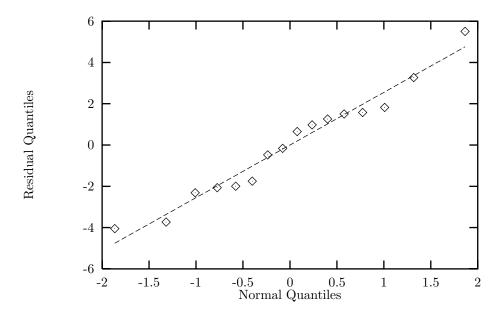

| 7.1        | Quantile-Quantile plot of residuals for four processor experiments                                                                         |

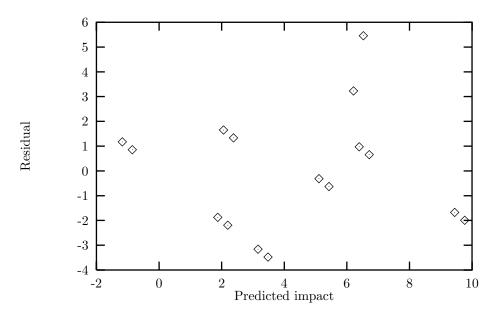

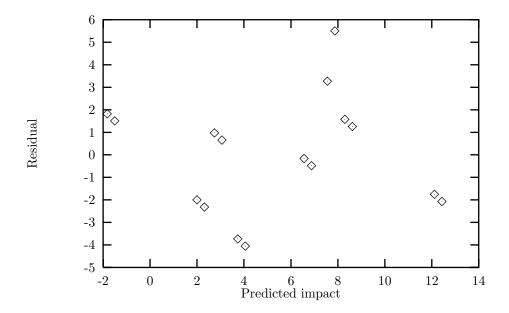

| 7.2        | Residual <i>vs.</i> Predicted value for four processor experiments                                                                         |

| 7.3        | Quantile-Quantile plot of residuals for sixteen processor experiments                                                                      |

| 7.4        | Residual <i>vs.</i> Predicted value for sixteen processor experiments                                                                      |

### LIST OF FIGURES

# List of Tables

| 3.1          | Comparison chart for invalidate coherency                                            | ) |

|--------------|--------------------------------------------------------------------------------------|---|

| 4.1          | Reference pattern for synth-FS with four processors                                  | 3 |

| $6.1 \\ 6.2$ | Summary of simulation runs for Barnes-Hut38Summary of simulation runs for Cholesky41 |   |

| 6.3          | Summary of simulation runs for Mp3d 45                                               | 5 |

| 6.4          | Summary of simulation runs for Water                                                 | 3 |

| 7.1          | Workload factors and the levels at which they are evaluated                          | L |

| 7.2          | Memory reference patterns for four processors                                        | 2 |

| 7.3          | Processor lists for reference pattern (2 2) 92                                       | 2 |

| 7.4          | List of all experiments for four processors                                          | 3 |

| 7.5          | Regression results for four processor experiments with all interactions 96           | ; |

| 7.6          | List of all experiments for sixteen processors                                       | 7 |

| 7.7          | Regression results for sixteen processor experiments with all interactions 99        | ) |

### LIST OF TABLES

# Chapter 1 Introduction

Efficiently supporting a shared memory paradigm in a large-scale multiprocessor generally involves some form of data caching. Data caching is an important technique to help reduce the effective memory reference latency and various forms of memory reference contention such as bus traffic and memory module contention. One of the drawbacks of caching shared data is the cost of keeping the multiple copies coherent.

One source of unnecessary coherency overhead is caused by a problem known as *false sharing* in large granularity cache units (e.g., multi-word cache lines or pages). False sharing is a result of co-location of unrelated data in the same line: The data may be used by different processors such that the line is shared among them but the individual data elements contained in the line are not each referenced by all these processors.

Informal definitions, such as this, attempt to capture intuitive notions of "bad" packaging of data relative to multiprocessor access patterns. Descriptions have varied considerably. At one extreme, informal false sharing definitions have included only *de facto* private data items residing together within a cache line (sharable, but actually accessed by different single processors). On the other hand, any access behavior falling short of a uniform, pure sharing pattern can be called false sharing. Unfortunately, the lack of a precise, universally accepted, definition of false sharing hinders research to detect and eliminate the problem.

In the next section, we describe previous attempts to characterize or solve the false sharing problem. We motivate the importance of false sharing by demonstrating the impact on coherency costs for real applications. In Section 2.1, we review some of the subtle issues that have made defining false sharing difficult and we articulate our intuition of false sharing. Section 2.3 formally defines our false sharing measures. In Chapter 3 we present our experimental methodology. In Chapter 4, we describe the sample programs we use in Chapter 5 and Chapter 6 to experimentally evaluate how well the measures capture our intuition and predict false sharing performance impacts. Finally, in Chapter 7 we determine the importance of the various workload and architectural factors on the impact of false sharing.

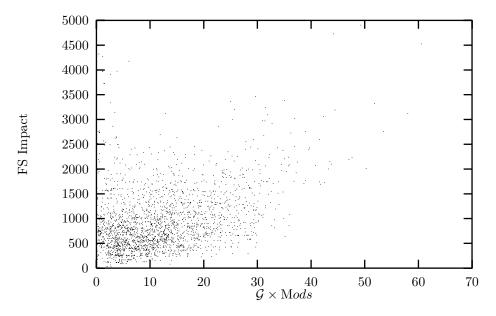

### **1.1** Evidence of the importance of false sharing

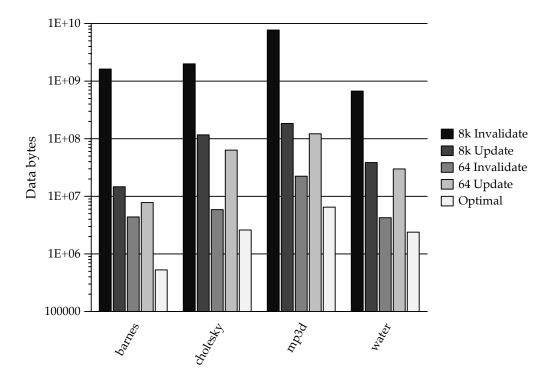

A first-order approximation to the cost of false sharing in the performance of a system is the amount of additional coherence traffic that it causes. Here we present results of a simple set of simulation experiments designed to measure the amount of coherence traffic caused by false sharing under typical cache coherence policies. These data serve to motivate our investigation of false sharing behavior by illustrating the seriousness of the false sharing problem and identifying some of the factors involved in finding a good definition.

The simulator used in our experiments is based on Tango [8] and is driven by the SPLASH

benchmarks [24]. We compare the performance of both update-based and invalidate-based coherence protocols to an optimal coherence mechanism. For these experiments we have written a machine description that is a simplified, parameterized NUMA<sup>1</sup> architecture in which the physical memories of each processor node act only as caches for the global virtual address space, sometimes referred to as COMA (Cache Only Memory Architecture). Each referenced virtual address is resident in the local memory cache of at least one processor node. To eliminate cache replacement effects, our simulator assumes infinite caches.<sup>2</sup> We simulate both 64-byte and 8192-byte cache line sizes. The 64-byte line size is reasonable in modern hardware-based caching systems, and the 8192-byte size is representative of systems based upon page-granularity caching (e.g., Galactica Net [27]).

Our primary metric is the number of data bytes transferred among the processors<sup>3</sup> in order to ensure cache coherence. For the invalidation-based coherence protocol, coherence traffic occurs when a processor misses on a line that would have been in the cache if it were not invalidated by a write to that line by some other processor. Our measurements do not include the traffic required to transmit invalidate messages when a shared line is modified. Coherence traffic for the update-based protocol consists of update messages sent to processors with copies of the line being modified. We count each destination independently, so that a single four-byte write to a shared location may result in the transfer of 4(n-1) data bytes if there are *n* processors sharing the updated line. Only data bytes are counted; all message overhead is ignored for both coherence protocols.

The optimal coherence policy that we simulate is based upon the following simple observation: When a value is written to a shared location, that value need only be propagated to processors that will actually read that value. It is obviously necessary to transfer a value written by one processor to any other that expects to read that value. Furthermore, it is easy to see that the data bytes transferred by this policy are sufficient, since any value that is never read by a processor cannot affect the outcome of that processor's computation. Since this policy generates both the sufficient and necessary coherence data traffic, it is optimal. A bit of reflection reveals that our optimal coherence policy is essentially an overhead-free invalidation-based coherence policy with single-word line size.

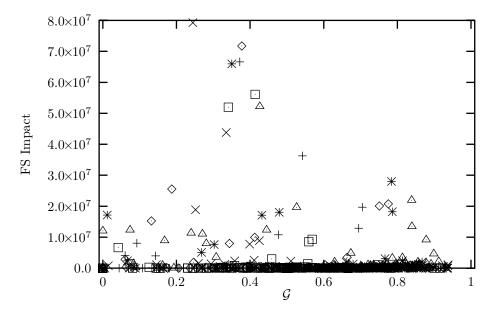

In Figure 1.1, we graph the results of our experiments. The data clearly show that the number of data bytes transferred to maintain coherence is significantly fewer for the optimal policy than for the four more realistic alternatives (note the logarithmic y-axis) in nearly all cases. Since the additional coherence traffic incurred by the realistic alternatives can be attributed to false sharing effects, these data clearly demonstrate the potential significance of false sharing, especially for page-based granularity caching systems.

### **1.2** Background

False sharing has been recognized as a serious problem in several recent studies. Some of the earliest uses of the term "false sharing" appear in discussion of memory management for NUMA architectures where page granularity migration and replication are employed to take advantage of the faster local memory access times [4, 2, 16]. False sharing has been blamed as a cause of increased coherency overhead in multiprocessor hardware caches with increasing line sizes in workload characterization studies of shared memory reference patterns [12, 11].

Techniques for ameliorating the false sharing problem have also been proposed in [7, 9, 1]. The solution provided by Munin [1, 6] addresses only the most conservative form of false sharing. Other proposals [7, 9] deal with the granularity of coherency which addresses one contributing

<sup>&</sup>lt;sup>1</sup>Non-Uniform Memory Access time.

<sup>&</sup>lt;sup>2</sup>This is a common simplification in cache studies.

$<sup>^{3}</sup>$ Note that we use "processors" and "caches" interchangeably when writing about the transfer of coherence data in a system.

Figure 1.1: Coherence data bytes transferred (real applications)

factor without necessitating (or offering) a thorough understanding or definition.

Two recent papers explicitly deal with quantifying false sharing effects and assessing proposed optimizations aimed at eliminating them [26, 10]. An important contribution of these papers is that each offers a concrete measure of false sharing *impact*. In each case, this is the number of false sharing cache misses. The measures subtly differ in how false sharing misses are identified and distinguished from misses caused by true sharing. The implementations result in a different way of counting the misses to be blamed on false sharing and a different categorization when applied to the same reference pattern. In [26], the method involves running two trace-driven simulations, one with single-word cache blocks and one with multi-word blocks. In an infinite single-word cache (i.e., no replacement), all misses (other than cold misses) result from coherency operations caused by true sharing. Cache misses that are present in the multi-word simulation that have no corresponding miss in the single-word simulation are attributed to false sharing. Some true sharing misses in the single-word simulation may also be eliminated in the multi-word simulation by successful prefetching. This technique is not amenable to real-time detection by an operating system. The mechanism for classifying misses as false sharing misses in [10] is based on tracking the current state (shared vs. non-shared) of referenced words, as determined by recent invalidation history, in a multi-word granularity trace-driven simulation. Both versions of this measure have the drawback that they depend on a particular coherency scheme (i.e., invalidation protocols) for the definition of false sharing. A definition that is less architecture dependent is highly desirable.

The real focus of these papers is on eliminating false sharing effects. Torrellas et al., in [26], discuss methods of reducing false sharing related cache misses. Their primary methods are to rearrange data such that variables that exhibit false sharing are placed on different cache blocks and to put variables protected by a lock on the same block as the lock. By applying

these optimizations to several applications, they were able to reduce the number of cache misses. Eggers and Jeremiassen [10] also propose techniques to eliminate false sharing in caches. Their transformations involve allocating data objects together that have similar sharing properties and the use of indirection.

Another effort aimed at defining and measuring false sharing is described in [3]. Bolosky and Scott consider a number of alternative formulations using the criteria that the definition should capture intuition, be mathematically precise, and be practical to apply. None of the alternatives is found to be satisfactory on all counts. However, this negative conclusion is in a sense inevitable since the intuitive notion the authors are trying to capture is not clearly articulated and the level of precision sought is unrealistic. Neither of the measures of false sharing used by Torrellas *et al.* [26] or Eggers and Jeremiassen<sup>4</sup> [10] were included in this study.

<sup>&</sup>lt;sup>4</sup>Although other aspects of this work were cited.

### Chapter 2

### **Proposed definition**

Detecting false sharing automatically requires some sort of metric to be defined. The "I'll know it when I see it"<sup>1</sup> detection method obviously cannot be automated. Our goals are (1) to detect when such a problem exists, (2) to identify the specific root causes of the problem (e.g., the data structures that don't belong together in a page based on having radically different access patterns or the processor(s) responsible for generating a different access pattern), and (3) to propose solutions that address the inherent causes (e.g., repackaging data, migrating processes). We address the first two of these issues in this thesis.

### 2.1 Difficulty of defining false sharing

The characteristics we desire in a definition (to be translated into a concrete measure) of false sharing are that it should (1) capture intuition, (2) be as architecturally independent as possible and yet at least loosely predict performance impacts for various architectures, and (3) have practical application in solving the false sharing problem.

The primary difficulty with providing a precise, formal definition of false sharing that captures intuition has been that the intuition has not proved easy to articulate. The only easily described intuitive notion (*de facto* private data items co-located in a shared line) seems clearly too narrow, although it is an interesting special case that yields to creative solutions (e.g., Munin's merge capability [6]) and is universally accepted as an example of false sharing. This case can be illustrated by the following trace of references for a line consisting of four words accessed by four processors. We denote the referenced word by an upper case letter, A-D, and the processor making the reference by a numeric subscript, 0-3 (e.g.,  $A_0$  represents processor 0's reference to word A):

$$A_0, B_1, C_2, D_3, B_1, D_3, C_2, A_0$$

Now consider the following trace which we claim also exhibits false sharing:

$$A_0, A_1, C_2, C_3, B_0, B_1, D_3, D_2$$

In this case, all words are shared, but only by different subsets of all the processors referencing the line as a whole (processors 0 and 1 reference words A and B while processors 2 and 3 reference C and D).

We need to be able to articulate the intuition that identifies such examples as forms of false sharing in order to derive and interpret more formal definitions or measures. This appears to be the missing step in all previous work. Consequently, we offer the following statement:

<sup>&</sup>lt;sup>1</sup>To paraphrase Supreme Court Justice Potter Stewart (though not to equate obscenity with false sharing).

The essence of false sharing is that the contribution made by the sharing patterns on individual words of a line toward the observed sharing pattern of the entire line is strictly less than full participation. Alternatively, the sets of processors accessing the individual words are proper subsets of the set of processors accessing the line and the level of false sharing is determined by the difference.

This statement covers various scenarios that we believe are examples of false sharing. It also translates into quantitative measures (in Section 2.3) that correspond to our intuitive feel for "more" or "less" false sharing in such scenarios.

Our second goal is architectural independence. As demonstrated in the previous section, using the difference between coherence costs of different architectures as the defining metric of false sharing is problematic is several ways. In particular, invalidation-based protocols and update-based protocols may yield very different results. One feature of such characterizations is a sensitivity to the precise ordering of references in a trace. The relative ordering of references from different processors is obviously a factor in quantifying false sharing impact, as illustrated by the difference between the following two reference strings under an invalidation-based protocol:

$$A_0, A_1, A_0, A_1, A_0, A_1$$

and

$$A_0, A_0, A_0, A_1, A_1, A_1.$$

The second reference string above is considered to be *sequentialized*: All references from a single processor occur prior to those of another processor. However, it is not clear that attending to minute reorderings between two traces that could be produced by the same program in an asynchronous parallel environment is desirable. We prefer a definition tied more to the program and line size and less to a particular execution of that program. Our measures define a window of observation in a trace and lose precise ordering information within that window. While choosing the window size is acknowledged to be an issue, losing some ordering information may be viewed as acceptable in that a particular trace is not attributed more precision than it is likely to deserve in a parallel system. It can also be argued that such summary information may be more practical for dynamic resource monitoring and management.

### 2.2 Definitions for factors

The following workload and architectural factors have been identified to affect the false sharing performance of a shared memory parallel program. All definitions for values that change during program execution implicitly cover only the interval of execution under study. The interval may be the entire execution of an application or may be some subset thereof. Intervals may be expressed either in units of time (such as microseconds) or in number of references (such as 5000 shared memory references).

- **Number of processors:** The number of processors participating in the computation. One processor/memory pair constitutes a single "node".

- **Page size:** The size, in bytes, of the virtual memory pages provided by the system under study. For systems with a fixed page size, this is an architectural parameter.

- **Remote memory reference latency:** The number of cycles required to reference a word on another node. On some architectures, this is not constant. It is not defined for systems which only do block copy operations.

#### 2.2. DEFINITIONS FOR FACTORS

- **Page copy time:** The number of cycles required to make a copy of a memory page on a node from another node. This may be shorter than the time needed to copy each word, since it can be achieved with a block-copy operation.

- **Coherency protocol:** The two policies we consider for keeping data coherent across nodes are *invalidate* and *update*. Invalidate coherency means that when one processor writes to a shared page, all other copies on other nodes are marked as invalid. When a node containing a page marked invalid needs to reference that page, it must fetch a new copy from a node with a valid copy. In the update coherence policy, when a page is modified on a node, all other nodes with a copy of the page get a message containing the new value for the modified word. The specific implementation details of these policies are not relevant here, since we are only concerned with the volume of data traffic not the time it takes to perform the coherency operations.

- **Update issue time:** The number of cycles required to send an updated value of a word from one node to another.

- **Update expire policy:** In the update coherency policy, all nodes with a copy of a given page need to be updated when any of them modifies a word in the page. Without some mechanism for removing inactive copies, unnecessary updates result and space is wasted. The expiration can be based on either time or reference counts. We choose the latter: It is defined as a number indicating how many updates for a given page a node will accept before it discards the page from its memory if there have been no intervening local references to that page.

- **Processor set size:** For any given word, the number of processors that read or write that word. For any given page, the number of processors that read or write any word in that page.

- Number of reads and writes: For any given word, the number of reads (or writes) made by all processors to that word. For any given page, the number of reads (or writes) made by all processors to any word in that page.

- Memory reference interleaving order: For a given word, the relative order in which each processor references that word in a global ordering.

If processor A references a word at absolute time  $t_A$ , and processor B references the same word at absolute time  $t_B$  where  $t_A \leq t_B$ , then the reference from processor A is before that from B. We denote this by the ordered list (A, B). The memory reference interleaving order is the ordered list resulting from the transitive closure of this relation for all references to the word from all processors.

We can extend this to the page or whole address space by replacing "word" in the paragraph above with "page" or "address space" respectively.

There are a few particular patterns of reference interleavings in which we are interested, primarily dealing with *locality of reference*. We base our definitions on the classical uniprocessor definition of locality from [13, Chap. 8].

*Temporal run:* If a word is referenced, it will tend to be referenced again soon by the same processor, without intervening references by another processor. The length of the run is the number of consecutive references by the processor.

With this definition, we attempt to capture the notion of a processor making exclusive use of a word for a period of time (locality in time). Thus, the memory reference interleaving order for a word would contain sequences of the form  $(\ldots, B, A, A, \cdots, A, A, C, \ldots)$ , i.e., containing a long sequence of references from only one processor. The following definitions deal with locality in space (memory locations).

- Cycles: The word is actively shared. The memory reference interleaving contains repeated references from a particular processor with references from other processors intermixed. The length of a cycle is the number of intervening references. For example, the trace excerpt  $(\ldots, A, x, x, A, x, x, A, x, x, A, \ldots)$  contains a cycle from processor A of length two (x indicates any processor other than A).

- Thrashing: Extreme manifestation of cycles. The word is shared between a subset of the processors, and the reference interleaving order contains interwoven cycles from these processors, resulting in cycles from each of these processors with an average length one less than the number of processors in the subset. For example, if the three processors A, B, and C are thrashing a word or page, the trace would contain segments of the form  $(\ldots, B, A, C, B, C, A, \cdots, B, A, C, \ldots)$ , where the average length of the cycles is two. During the period of thrashing, no other processor references that word.

Unstructured: Memory reference orderings that do not have one of the above structures.

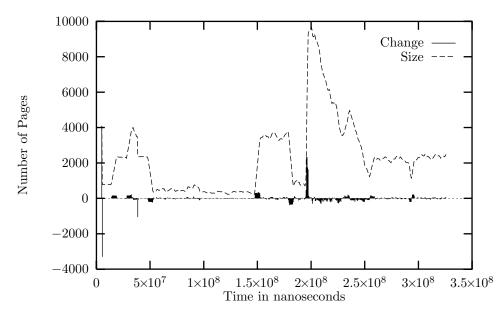

- Working set: Traditionally, it is the set of pages in a process's virtual address space to which memory references have been made over some period of time [18]. We extend this definition to be the set of pages to which memory references have been made from any processor, and restrict the references counted to the shared data pages. Suggested periods of time are the last 10,000 instructions or 10ms [19].

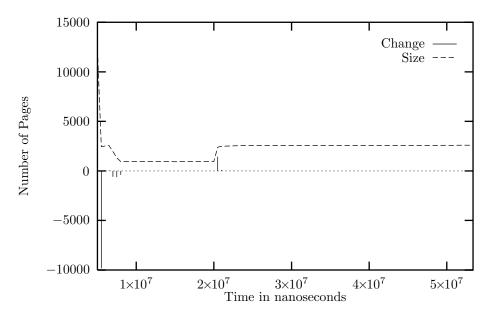

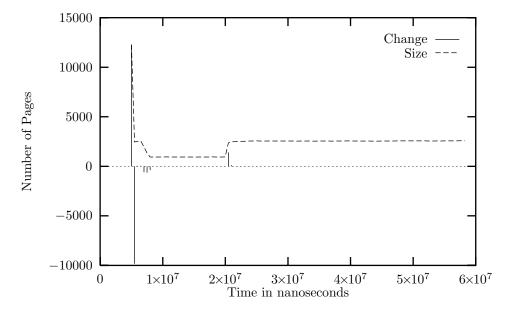

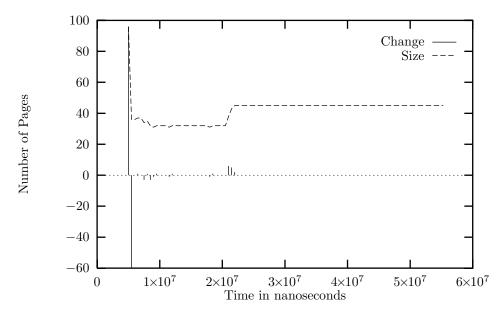

- **Phase change:** The reference patterns dramatically change between "phases" of execution, such as between initialization and computation phases of a numerical computation. Formally, it is when the rate of change in the working set for a given processor is higher than the local average rate of change. This may be exhibited as a sudden burst in the size of the working set.

- **Sharing participation:** The degree to which the set of processors referencing a particular word in a page is different from the set of processors referencing any word in that page. This is quantitatively defined by the  $\mathcal{F}$  metric in Equation 2.4. The  $\mathcal{G}$  metric from Equation 2.6 quantifies the participation for the entire page.

The definitions presented for working set and phase change are provided only to be able to define analysis interval boundaries. The significance of each of these factors in false sharing impact is the subject of Chapter 7. Since our cost metric is based on data bytes transferred over the interconnection network, we keep the timing-based factors fixed throughout our experiments.

### 2.3 Measures for false sharing

The coherence traffic cost measure of the previous chapter quantifies the *impact* of false sharing, but only indirectly suggests the degree of false sharing caused by the particular composition and sharing patterns applied to the page or line. In this section, we define more direct measures for false sharing that capture the intuition expressed in Section 2.1. These are based on shared-memory reference traces but are independent of any coherence mechanism.

Initially, each referenced word is assigned a false sharing value. These values are then combined to calculate a measure for each line. This measure is useful in helping to isolate where false sharing is taking place.

We define our false sharing measure based on a basic unit of memory reference, which we will call a word (w). The size of a word is not defined here, and in fact may not be of fixed size. Typically, references come in two sizes of a single word (4 bytes) and a double word (8 bytes). We use the term *word* to refer to all atomic memory references, regardless of their actual size. Words that are not referenced are treated as if they do not exist, since unreferenced words have no direct effect on memory coherence costs.

#### 2.3. MEASURES FOR FALSE SHARING

The unit of memory coherence is a line (l) which is a set of words:

$$l_{j} = \{w_{i} | \text{word } i \text{ is part of line } j\}$$

$$l_{i} \cap l_{k} = \emptyset, \ j \neq k$$

$$(2.1)$$

In our discussion, we also refer to lines as pages, since page-granularity coherence motivated this work.

The number of references made to word  $w_i$  is denoted  $w_{i,r}$  and the number of write-references (modifications) is denoted  $w_{i,m}$ . Similarly, we denote the total number of references to line  $l_j$  as  $l_{j,r}$  and the number of write-references to the line as  $l_{j,m}$ . All of these counts are taken over the interval of time that is under study (this may be the entire duration of execution.)

The *processor set* of a word is the set of processors that reference the word over the time interval of interest:

$$W_i = \{ \text{processors referencing } w_i \}$$

(2.2)

The processor set of a line is the union of the processor sets of the words in the line:

$$L_j = \bigcup_{w_i \in l_j} W_i \tag{2.3}$$

$= \{ \text{processors referencing } l_j \}$

Using these definitions, we can derive an expression for the false sharing that can be attributed to a particular  $w_i$  in  $l_j$ :

$$\mathcal{F}(i,j) = 1 - \frac{|W_i|}{|L_j|} \tag{2.4}$$

The key idea being that the greater the difference between the word's processor set size and the line's processor set size, the greater the degree of false sharing associated with that word. If a word has not been referenced, we do not use it in any further calculations.

For most cache coherence schemes, the primary cause of coherence overhead is due to write references. With an invalidation-based protocol, writes cause the invalidations that in turn can cause false sharing misses, and in an update-based protocol, it is the write references that cause false sharing updates. Thus, it is often useful to weight  $\mathcal{F}(i, j)$  by the fraction of references to  $w_i$  that are writes:

$$\mathcal{F}'(i,j) = \mathcal{F}(i,j) \times \frac{w_{i,m}}{w_{i,r}}$$

(2.5)

so that words used in a mostly read-only fashion will have  $\mathcal{F}'(i, j)$  close to zero, while words with high write-to-reference ratios will have  $\mathcal{F}'(i, j)$  values closer to  $\mathcal{F}(i, j)$ .

The definition for false sharing associated with a given line is:

$$\mathcal{G}(j) = \sum_{w_i \in l_j} \mathcal{F}(i,j) \times \frac{w_{i,r}}{l_{j,r}}$$

(2.6)

which is just the weighted average of the false sharing measures of the individual words in the line. To see the importance of the weighting, consider a line with n words, one of which has a very high  $\mathcal{F}(i, j)$  value and the rest with no false sharing (i.e.,  $\mathcal{F}(i, j) = 0$ ). Clearly, if there are very few references made to the one falsely-shared word, we would not consider the line to be heavily falsely-shared. On the other hand, if the majority of references to the line were to that one word, we would definitely consider the line to be falsely-shared. The weighting makes it possible to distinguish these situations from one another.

As in the per-word case, we also define a write-weighted version of this measure:

$$\mathcal{G}'(j) = \sum_{w_i \in l_j} \mathcal{F}'(i,j) \times \frac{w_{i,r}}{l_{j,r}}$$

$$= \sum_{w_i \in l_j} \mathcal{F}(i,j) \times \frac{w_{i,m}}{l_{j,r}}$$

(2.7)

The weighting adjusts for the different contributions of each word to the overall false sharing associated with the line.

### 2.4 Summary

In this chapter we reviewed the intrinsic and previously encountered difficulties in previous attempts to define false sharing. We then presented our intuitive notion of false sharing and the characteristics that a good definition for false sharing must have. In preparation for defining our measure of false sharing, we defined the workload and architectural parameters that affect false sharing. Finally, we developed in detail the measures we propose as candidates to be evaluated for their usefulness in defining and predicting false sharing.

### Chapter 3

### **Experimental Methodology**

To evaluate the proposed measures, we need a testbed in which we can easily modify architectural parameters and collect memory reference traces. We need traces in order to accurately measure the actual false sharing, true sharing, and prefetching that occurs. Using a multiprocessor execution-driven simulator allows us these capabilities.

The simulation environment we use is Tango [8] with our own machine model description. Tango allows us to run each program multiple times with the same input and generate trace files which are based on the specific architectural parameters under study. Trace driven simulation would not suffice, as evidenced by the radical difference in execution times and number of memory references in the Barnes-Hut program from the SPLASH benchmark suite (see Section 6.1.1). In this program, a change in the type of memory coherence from update to invalidate caused the run time of the program to increase by more than three times. The potential inaccuracy of trace-driven simulations is one of the reasons for which Tango was originally written. Holliday and Ellis [14] discuss the accuracy of such studies.

### 3.1 The simulator

Tango simulations are built such that a single executable contains both the simulation environment and the application program. When the program is run, the simulator reads the necessary parameters from a configuration file, allocates the system resources it will need, and finally creates the parallel environment. It then transfers control to the main routine of the application.

Programs are written using the Argonne PARMACS macros [5]. At compile time, the appropriate hooks into the Tango libraries are inserted into the application object code. As much of the code as can be is directly executed by the host CPU. For code that makes shared-memory references, the Tango simulator code calls a routine in our NUMA simulator to determine how long the reference will take. At this time, the status of the referenced page is updated.

#### 3.1.1 The machine we are modeling

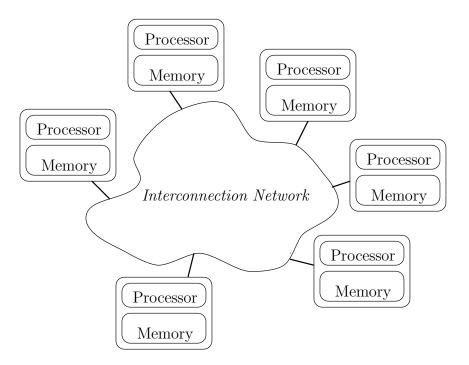

The machine we model consists of multiple processor-memory pair nodes connected by an arbitrary network (Figure 3.1). The network is used to implement the coherent shared memory abstraction for running MIMD (multiple instruction, multiple data) programs. A MIMD program runs on multiple processors, with each processor progressing independently of the others, except at explicit synchronization points. Remote memory references are more expensive than local ones (NUMA) and each node's memory serves as a cache for the global virtual address space — there is no centralized global memory. Every reference must go to physical memory since there are no instruction or data caches. Each node is assumed to have enough physical

Figure 3.1: Idealized NUMA shared memory architecture

memory to hold all the virtual memory pages it will need so we don't have to worry about page-replacement policies.<sup>1</sup> For these studies, all remote references are handled by replicating the referenced page onto the local memory.

### 3.1.2 Architecture parameters

There are six options that modify the architecture of the machine being simulated. These parameters allow for a very large number of qualitatively different architectures to be evaluated. The options controlling the parameters are read from a configuration file by the simulator at start-up, along with the other standard Tango parameters that set the time needed to execute each instruction and reference local memory.

The simulator can run either an invalidate-based or an update-based memory coherency policy. Invalidate coherency means that when one processor writes to a shared page, all other copies on other nodes are marked as invalid. When a node containing a page marked invalid needs to reference that page, it must fetch a new copy from a node with a valid copy. In the update coherence policy, when a page is modified on a node, all other nodes with a copy of the page get a message containing the new value. This keeps all copies of the pages in the system identical. The coherency policy is selected by the CacheType parameter.

In either update or invalidate coherency, we use a sequential consistency model. Sequential consistency implies that any changes to global memory are visible to all processors simultaneously and before *any* future references are made. This affects our studies in that every coherency operation causes traffic. In other consistency models, the coherency operations can be delayed and batched together to reduce overheads when it is known that a particular word will not be used by the target node during the delay. Other memory consistency models are discussed in

<sup>&</sup>lt;sup>1</sup>A common simplification in cache studies.

[20].

For the update memory coherency policy, another parameter limits the number of "useless" updates sent to a node. If a page on a node has not been used locally for a while, it is expired (marked as invalid) so future modifications to that page on other nodes will not send additional updates to the node. This reduces network traffic for pages which are no longer used by a given node. The threshold used to determine when to expire a page in this situation is determined by the following formula [17]:

$$C \times T_u = T_p \tag{3.1}$$

The value C is the count of the number of updates sent to the node for the page in question,  $T_u$  is the time required to send an update for one word, and  $T_p$  is the time needed to copy an entire page from another node. Since the latter two are fixed by the architecture, we can easily compute C for our simulations. When a node has received C updates for a page without referencing it locally, it will expire the page. The UpdThresh parameter determines the C value. If this value is set to zero, the pages are never expired in this manner.

The size of the virtual memory pages can be set to any power of two from one word up to 8192 bytes (PageSize). The number of processors being simulated must also be set (NumNodes). Only one thread runs per processor node.

As part of its operation, the memory system will need to copy an entire page from one node to another. On a real machine, this can be done with a block copy if the hardware supports it, or with a word-by-word copy loop implemented in software. Two parameters in the simulator allow for maximum flexibility in deciding how block copies are done. The first parameter adjusts the size of a block transfer (BlockSize). This can be anywhere from a single word up to PageSize, but must divide PageSize evenly. The other parameter sets the time needed to transfer a single block across the network (BlockCost). Setting these parameters to a single word sized block and a transfer cost equal to that of a remote memory reference would simulate a machine with no hardware block transfer capability.

In our experiments, BlockCost is set to 200.0 and BlockSize is set to 64 bytes, except in the cases where the PageSize is four: BlockCost is set to 20.0 and BlockSize set to 4 bytes. CacheType, PageSize, and NumNodes are varied for the different experiments. For the 64-byte page size experiments, UpdThresh is computed as 10, and for the 8192-byte page size experiments, it is computed as 1280.

#### 3.1.3 Detailed operation of the simulator

Every reference to shared memory results in Tango calling a routine in our NUMA simulator to compute the latency<sup>2</sup> of the reference. In this procedure we track the status of each word and page in the shared memory space for each node. Every page from the shared address space is in one of three states on each node:

unaccessed The page has never been accessed by this processor.

valid There is a copy of this page in the local memory.

invalid The copy of the page on this node has been invalidated.

The initial access to a page by a processor brings the page from unaccessed state to valid state and is counted as a cold miss. Data transfer costs associated with a *cold miss* are not used in our analysis. A reference to a page which is marked invalid for the processor is counted as an *invalidate miss* and brings the page to the valid state. If the reference is a write, then copies of the page on all other processors are marked as invalid for the invalidate protocol (by sending a message to each processor with a copy), or an update message containing the new value is sent to each processor holding a copy of the page for the update protocol.

$<sup>^{2}</sup>$ time to complete

Messages are not really sent—just a count of how many and of which type is kept. There is no overhead cost associated with these messages since we are interested primarily in the amount of data traffic over the network. However, since we know the exact count of messages delivered, we can add in this overhead at a later time during analysis.

The memory system simulated always does a page replication for non-local memory references. If a replication is necessary, the time taken to satisfy the read or write is equivalent to the time it takes to transfer PageSize ÷ BlockSize blocks at BlockCost time for each. We do not model any contention for the transport network. If a reference is local because the page is in the node's local memory, the time taken is the same as any other local memory reference. In the update coherency case, once a page is replicated on a node it is always sent updates regardless of whether it will actually use the page again.

The output from the simulator is a trace of all references to the global memory space. The code and private data segment references are ignored since they are assumed to be in a private area of each node's memory and cannot affect the cost of data communication. The trace format consists of one machine-independent trace file per simulated processor, where each trace entry consists of the following fields:

- address space (shared or private)

- processor node number

- type (read or write)

- length (number of bytes)

- time

- address

During analysis, the traces from each processor are merged and sorted by reference time. This provides us with a trace of the global memory reference interleaving order.

### 3.2 Calculating true costs

The traces collected when running the simulations are used to calculate the actual false sharing and true sharing costs as well as the amount of benefit due to prefetching on a per-page basis. These calculations are done off-line since there is a considerable amount of state information necessary, and in some cases we need to know what the future references are.

### 3.2.1 Invalidate Coherency

The technique used is similar to the one used in [25], but we calculate the bytes transferred due to false sharing rather than just counting the false sharing misses. Two concurrent trace driven simulations are run: one is identical to the simulation that generated the trace (multi-word line size), and the other tracks the location and status of each shared word (single-word line size). On each shared memory reference, both simulations are updated, and the result (hit or miss) from each is compared.

In Table 3.1 are listed the four possibilities of the comparison. If the single-word simulation resulted in a hit and the multi-word simulation indicated a miss for a reference, then we would conclude that the miss was induced by false sharing, and thus add to the false sharing cost the amount of data we needed to transfer across the network (the size of a page). The other cases contribute nothing to the false sharing cost calculation. The simulator is capable of distinguishing a cold and true sharing miss by setting an additional flag.

| single-word          | multi-word           | indication                 |

|----------------------|----------------------|----------------------------|